#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción/Repaso

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

#### Clase 2:

## Descripción de la funcionalidad

#### 2.1 Introducción/Repaso

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

### Introducción

-- Multiplexor de dos entradas MUX21 entity mux21 is e1 01 port ( e1, e2: IN std\_logic; sel: IN std logic; e2 ol: OUT std\_logic); sel end mux21: arquitecture A of mux21 is begin process(e1,e2, sel) **MUX21** begin e1 **if** (sel= '0') **then**  $o1 \le E1;$ 01 e2 else  $o1 \le e2;$ endif; sel end process; end A;

# Introducción. Formas de describir una ARCHITECTURE

- Dos formas distintas :

- 1. Órdenes concurrentes: Ejecución de órdenes en parelelo.

- 2. Utilizando *process:* Dentro de un process las órdenes se ejecutan de forma secuencial.

Es posible combinar ambas en una misma ARCHITECTURE

#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

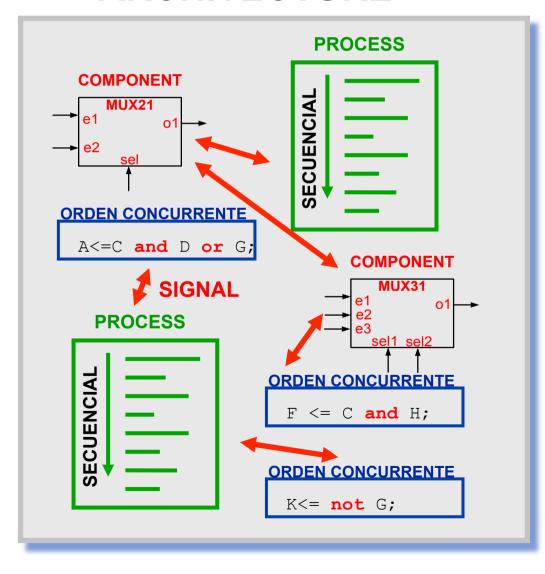

# Concepto de concurrencia

#### **ARCHITECTURE**

Sentencias concurrentes: Órdenes independientes que se ejecutan en paralelo.

```

\begin{tabular}{ll} A<=C \ and \ D \ or \ G; \\ F <= A \ when \ E='0' \ else \ 'H'; \\ \end{tabular}

```

PROCESS: Conjunto de órdenes que se ejecutan de forma secuencial.

```

process(e1,e2, sel)

begin

if (sel='0') then

o1 <= E1;

else

o1<= e2;

endif;

end process;</pre>

```

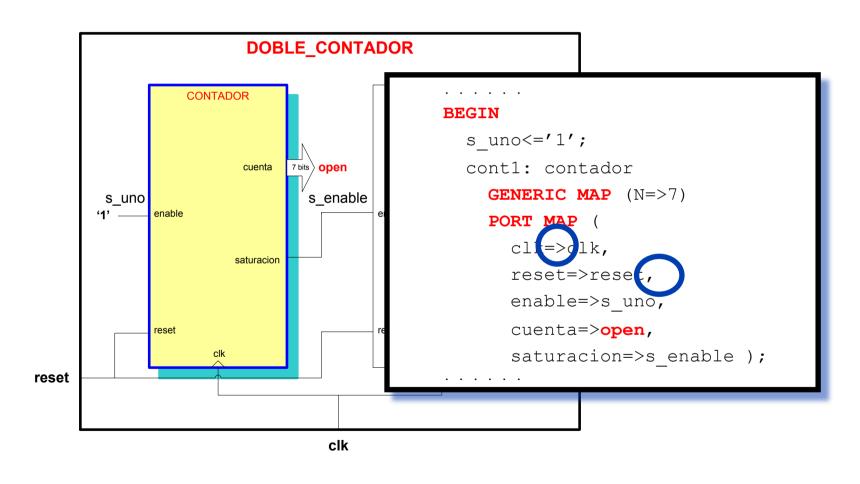

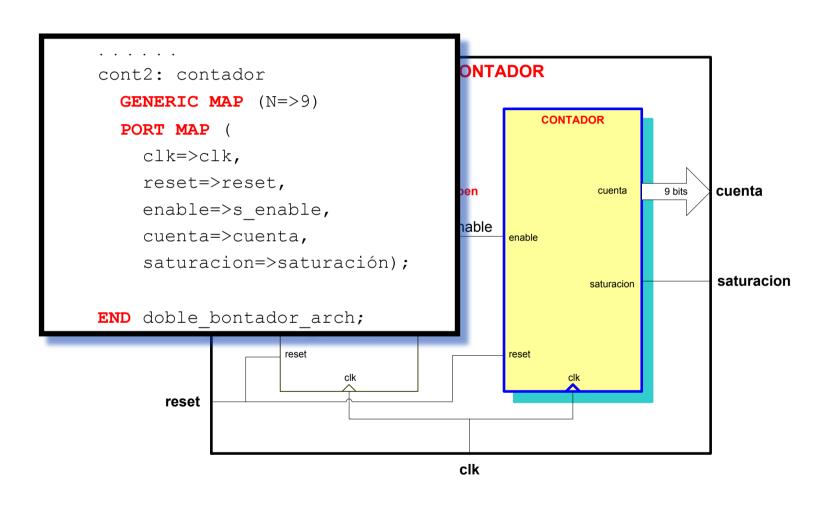

INSTANCIAS A COMPONENTES: Cada componente será un bloque que funcionará en paralelo

```

cont1: contador

GENERIC MAP (N=>7)

PORT MAP ( ......)

```

- Por naturaleza, todos los elementos de un circuito funcionan de forma concurrente.

- Todas las sentencias fuera de un process se ejecutan de forma paralela.

- ◆ El orden de las sentencias no es importante.

- Un componente se entiende como otra sentencia concurrente.

- Un process se comporta externamente como una sentencia concurrente.

# Concepto de concurrencia

#### **ARCHITECTURE**

- Todas las órdenes dentro de un process se ejecutan secuencialmente, pero externamente se comporta como una sola orden concurrente.

- Un componente se entiende como otra sentencia concurrente.

- Los diferentes elementos se comunican utilizando signals

#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción

- 2.2 Concepto de concurrencia

#### 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

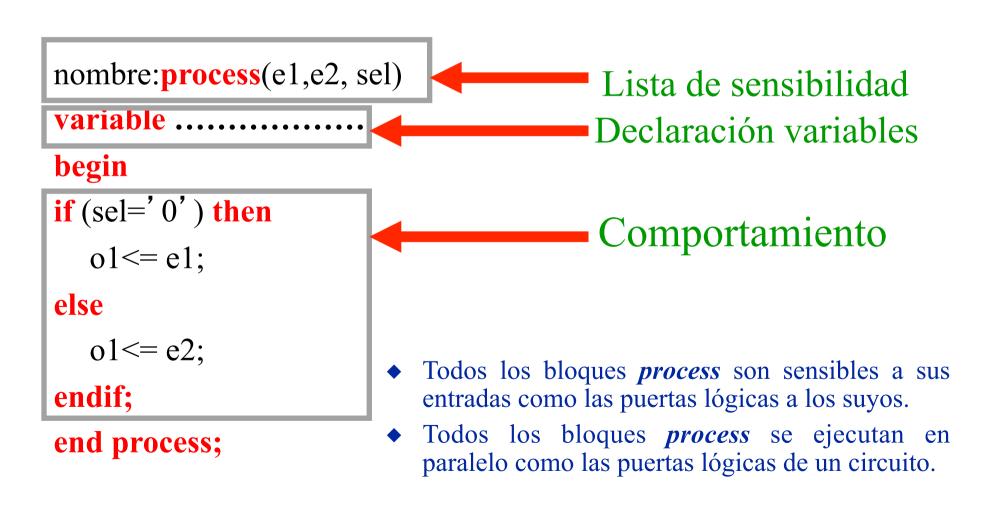

### **Proceso**

El bloque process como unidad básica de ejecución.

## Proceso. Lista de sensibilidad

El proceso se ejecuta en su totalidad cuando cambia algunas señal de la lista de sensibilidad

```

proc1: process (a,b,c)

begin

x <= a and b and c;

end process;</pre>

```

```

proc2: process (a,b)

begin

x <= a and b and c;

end process;</pre>

```

- ◆ Desde el punto de vista de simulación, ambos procesos son muy diferentes.

- ◆ El *proc2* no es sintetizable (faltará un latch para c que es sensible a ambos flancos de a y b), por tanto:

- El programa de síntesis añadirá la señal c a la lista de sensibilidad para poder asociar un circuito al código.

- El programa de síntesis produce un mensaje de error.

## Proceso. Lista de sensibilidad

CONCLUSIÓN: En un código VHDL para síntesis de un proceso combinacional, en la lista de sensibilidad deben incluirse todas las señales que afecten a la evaluación del proceso.

- Un proceso sin lista de sensibilidad se estaría ejecutando siempre, por tanto el simulador nunca avanzaría.

- Si una señal de la lista de sensibilidad cambia el proceso es evaluado sucesivamente hasta que todas las señales sensibles se estabilicen.

# Proceso. Asignación de señales

- ◆ Todas la expresiones de un proceso se resuelven con el valor actual de las señales.

- ◆ Las asignaciones se hacen efectivas cuando se termine la evaluación del proceso.

- ◆ Todas las señales serán actualizadas con el último valor asignado dentro del proceso.

- ◆ El proceso vuelve a evaluarse si se ha modificado alguna señal de su lista sensible.

- ◆ Todos los procesos cuya lista sensible ha sido alterada y todas las órdenes concurrentes se ejecutan hasta que se alcanza un estado de equilibrio (no hay más cambios).

### Proceso. Asignación de señales (ejemplo 1)

#### Diferentes opciones para implementar el mux2

```

process(e1,e2, sel)

begin

if (sel='0') then

o1<= e1;

else

o1<= e2;

endif;

end process;</pre>

```

```

process(e1,e2, sel)

begin

o1<= e1;

if (sel=' 1') then

o1<= e2;

endif;

end process;</pre>

```

```

process(e1,e2, sel)

begin

if (sel='1') then

o1<= e2;

endif;

o1<= e1;

end process;</pre>

```

## <u>INCORRECTO</u>

O1 siempre valdrá e1

#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

### Sentencias concurrentes. Asignación simple

```

señal_destino <= señal_origen;</pre>

```

- Deben ser del mismo tipo (integer, std\_logic, etc)

- señal\_destino puede ser:

- Señal

- Puerto: OUT, INOUT (y BUFFER)

- señal\_origen puede ser:

- Señal

- Puerto: IN, INOUT ( y BUFFER)

#### PUEDEN USARSE DENTRO O FUERA DE UN PROCESS

### Sentencias concurrentes. Ecuaciones lógicas

| Operador     | Ejemplo            |

|--------------|--------------------|

| NOT          | a <= <b>NOT</b> b; |

| AND, NAND    | a <= b AND c;      |

| OR, NOR, XOR | a <= b OR c AND d; |

#### PUEDEN USARSE DENTRO O FUERA DE UN PROCESS

### Sentencias concurrentes. Ejemplo

```

library IEEE;

use IEEE.std logic 1164.all;

entity mux21 is

port ( e1, e2: IN std logic;

sel: IN std logic;

o1: OUT std logic);

end mux21;

arquitecture A of mux21 is

begin

o1 <= e1 and not(sel) or e2 and sel;</pre>

end A;

```

#### Sentencias concurrentes. WHEN .... ELSE ....

Señal Destino <= Expresión1 WHEN Condición ELSE Expresión2;

```

Señal Destino <= Expresión1 WHEN Condición1 ELSE

Expresión2 WHEN Condición2 ELSE

Expresión3 WHEN Condición3 ELSE

....

ExpresiónN WHEN CondiciónN

ELSE Expresión;

```

#### NO PUEDEN USARSE DENTRO DE UN PROCESS

#### Sentencias concurrentes. WHEN .... ELSE ....

```

library IEEE;

use IEEE.std logic 1164.all;

entity mux21 is

sel: IN std logic;

o1: OUT std logic);

end mux21;

arquitecture A of mux21 is

begin

o1 <= e1 when sel='0' else e2;

end A;

```

#### Sentencias concurrentes. WITH ... SELECT ...

```

WITH sel SELECT

o1 <=

e1 WHEN '0',

e2 WHEN OTHERS;</pre>

```

NO PUEDEN USARSE DENTRO DE UN PROCESS

#### Clase 2:

## Descripción de la funcionalidad

- 2.1 Introducción

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

# IF THEN ELSIF ELSE

#### NO PUEDEN USARSE FUERA DE UN PROCESS

# IF THEN ELSIF ELSE

## **CASE WHEN**

```

CASE objeto IS

WHEN caso1 =>

Código1;

WHEN caso2 =>

Código2;

WHEN caso3 =>

Código34;

WHEN OTHERS =>

Código;

END CASE;

```

NO PUEDEN USARSE FUERA DE UN PROCESS

## **CASE WHEN**

WHEN OTHERS es obligatorio si no están cubiertos todos los casos

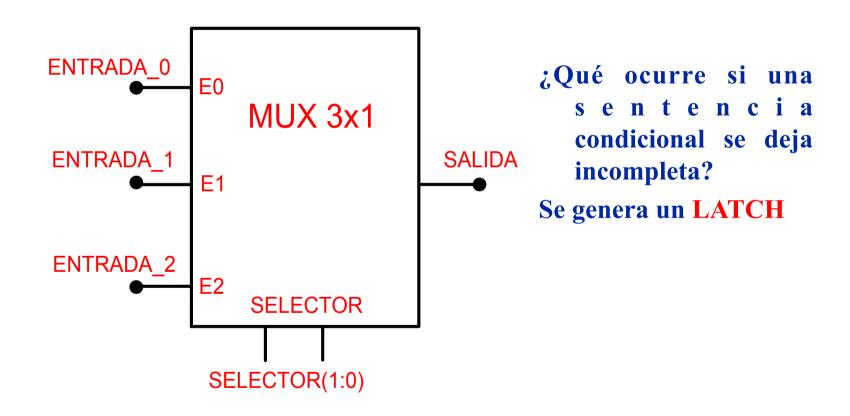

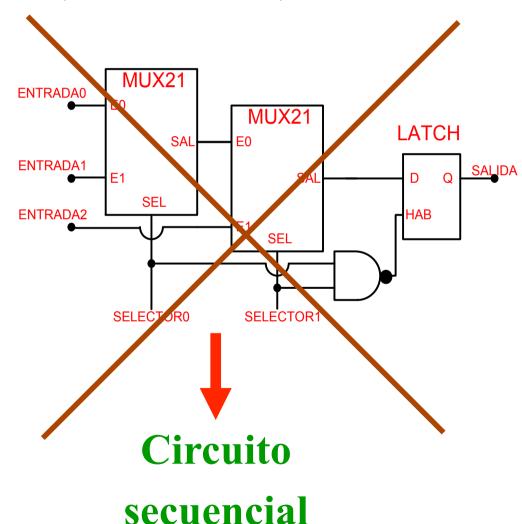

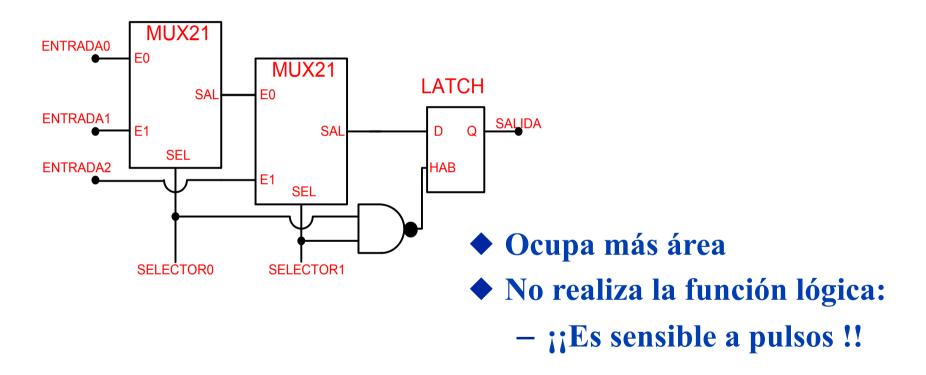

### Generación de LATCHES

#### Ej. Multiplexor 3x1

## Sentencias condicionales incompletas.

**♦** No se define la condición (*selector*="11")

# Programación

```

if (selector="00") then

salida<=entrada_0;

elsif (selector="01") then

salida<=entrada_1;

elsif (selector="10") then

salida<=entrada_2;

endif;</pre>

```

## Sentencias condicionales incompletas.

#### Circuito con un latch

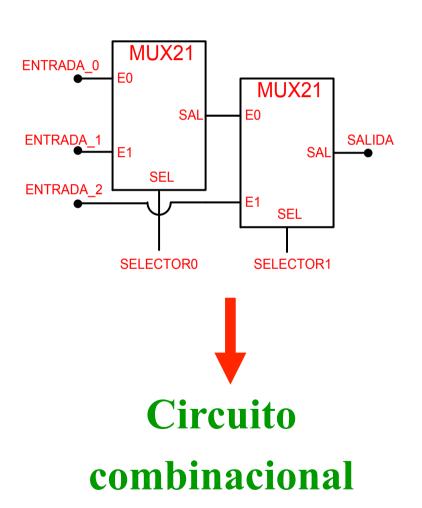

## Sentencias condicionales incompletas.

Código correctoDescripción

```

if (selector="00") then

salida<=entrada 0;

elsif (selector="01") then

salida<=entrada 1;

elsif (selector="10") then

salida <= entrada 2;

else

salida<=entrada 2;

end if;

```

## Circuitos combinacionales y secuenciales.

#### **Conclusiones**

- **◆** Los circuitos combinacionales deben estar completamente especificados.

- ◆ Se genera una celda de memoria siempre que:

- No se especifica el valor de la salida para todos los posibles valores de las entradas

- **◆** Un latch es un circuito muy sensible a pulsos y timing:

- Sólo debe ser utilizado en casos concretos.

## Driver de una pantalla de 7 LEDs Ejemplo diseño combinacional

```

LIBRARY IEEE;

USE IEEE.std logic 1164.all;

ENTITY bit2led IS

PORT (

bits: IN STD LOGIC VECTOR (3 downto 0);

led: OUT STD LOGIC VECTOR (6 downto 0)

);

END bit2led;

ARCHITECTURE bit2led_arch OF bit2led IS

BEGIN

-- contenido de la arquitectura

END bit2led_arch;

```

## Driver de una pantalla de 7 LEDs Ejemplo diseño combinacional

```

async bit: PROCESS(bits)

BEGIN

CASE bits IS

WHEN "0001" =>

LED <= "0000110"; --1

WHEN "0010" =>

LED <= "1011011"; --2

WHEN "0011" =>

LED <= "1001111"; --3

WHEN "0100" =>

LED <= "1100110"; --4

WHEN "0101" =>

LED <= "1101101"; --5

WHEN "0110" =>

LED <= "1111101"; --6

WHEN "0111" =>

LED <= "0000111"; --7

WHEN "1000" =>

LED <= "11111111"; --8

```

```

WHEN "1001" =>

LED <= "1101111"; --9

WHEN "1010" =>

LED <= "1110111"; --A

WHEN "1011" =>

LED <= "1111100";

--b

WHEN "1100" =>

LED <= "0111001"; --C

WHEN "1101" =>

LED <= "1011110"; --d

WHEN "1110" =>

LED <= "1111001"; --E

WHEN "1111" =>

LED <= "1110001"; --F

WHEN OTHERS =>

LED <= "01111111"; --0

END CASE;

END PROCESS;

```

#### Tema 4:

## Descripción de la funcionalidad

- 2.1 Introducción/Repaso

- 2.2 Concepto de concurrencia

- 2.3 Procesos

- 2.4 Diseño de circuitos combinacionales

- 2.4.1. Sentencias concurrentes

- 2.4.2. Descripción mediante procesos

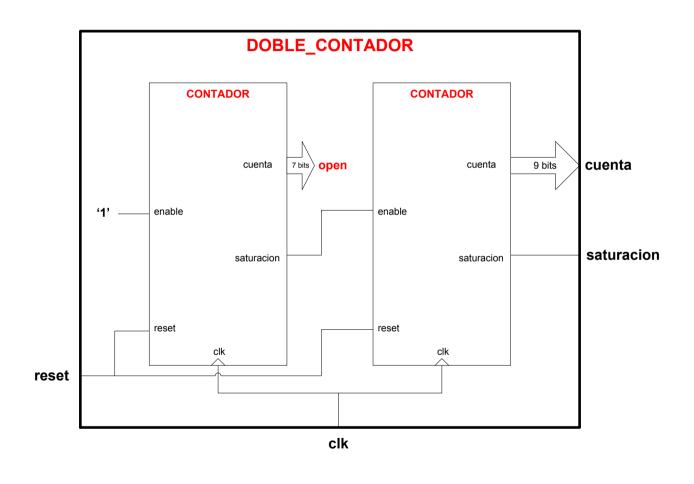

- 2.5 Interconexión de componentes

### La sección ARCHITECTURE. Componente

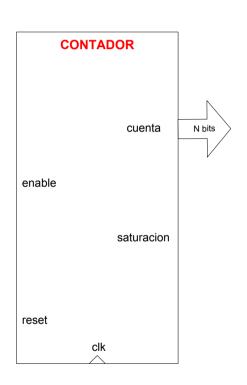

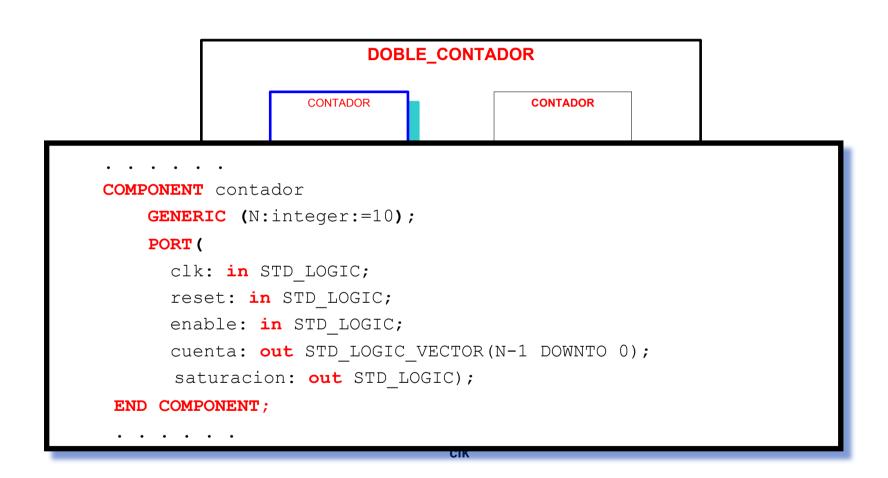

- ◆ Componente: entidad de un orden inferior de jerarquía

- ◆ Sintáxis:

```

component nombre

generic (definición de gererics);

port ( definición de puertos);

end component;

```

```

nombre_instancia : nombre_componente

GENERIC MAP(.....);

```

Declaración del componente.

En la zona de declaraciones de señales y componentes

Utilización del componente.

Dentro del cuerpo de la arquitectura (BEGIN)

**Objetivo**

Previamente debemos haber diseñado el nivel de jerarquía inferior

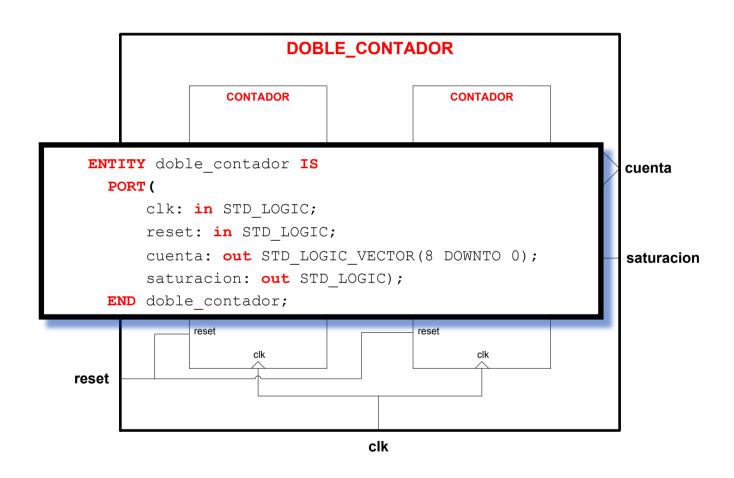

PASO 1: Definir la entidad de DOBLE CONTADOR

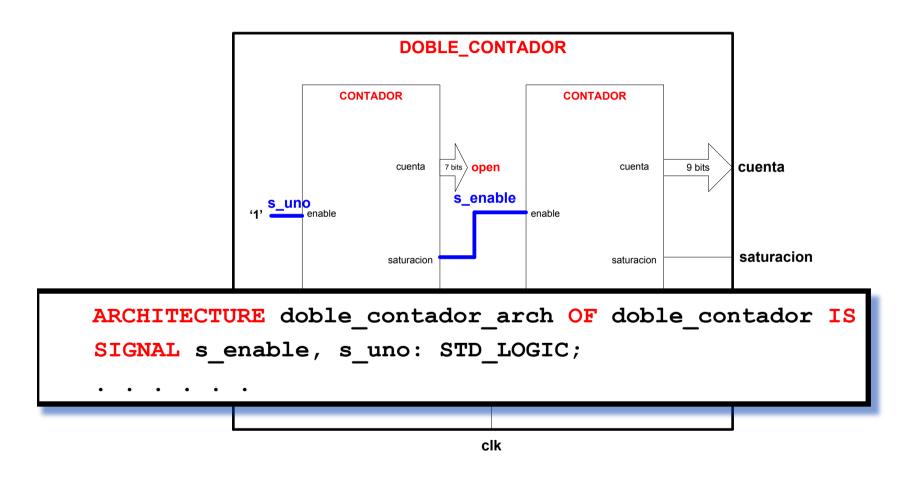

PASO 2: Declarar las señales necesarias (cables que no salen al exterior)

PASO 3: Declarar los componentes necesarios (entidades del nivel de jerarquía inferior)

PASO 4: Realizar la instancia (llamada) al primer contador. (dentro del BEGIN)

PASO 4: Realizar la instancia (llamada) al segundo contador.

#### **DEBERES**

- La próxima clase será la más importante de VHDL. REPASAR LO VISTO HASTA AHORA ANTES DE LA CLASE.

- Instalar el software de la asignatura.

- ◆ Usaremos el ISE, de Xilinx

- Página de descarga:

http://www.xilinx.com/support/download/index.htm