# VHDL PARA DISEÑO Y VALIDACIÓN DE SISTEMAS DIGTALES

Jonathan Noel Tombs

Miguel Ángel Aguirre Echánove

Fernando Muñoz Chavero

Hipólito Guzmán Miranda

Universidad de Sevilla Mayo de 2016

# Contenido

| CAPÍ                                     | TULO I. LENGUAJES DE DESCRIPCIÓN DE HARDWARE         |    |

|------------------------------------------|------------------------------------------------------|----|

| 1.                                       | Introducción histórica                               |    |

| 2.                                       | Los HDL's en la metodología de diseño.               |    |

| 3.                                       | Jerarquía de un diseño.                              |    |

| 4.                                       | Niveles de abstracción de un HDL                     |    |

| 5.                                       | HDL: Programa o diseño.                              |    |

| 6.                                       | Lenguajes HDL                                        |    |

| 7.                                       | Síntesis de Circuitos.                               | 11 |

| CAPÍ                                     | TULO II. ESTRUCTURA DE UN BLOQUE FUNCIONAL EN VHDL   | 14 |

| 1.                                       | Cuestiones previas                                   |    |

| 2.                                       | Un primer ejemplo en VHDL                            | 14 |

| 3.                                       | Estructura de un diseño VHDL                         | 18 |

| 4.                                       | La sección ENTITY                                    |    |

| 5.                                       | La sección ARCHITECTURE                              | 22 |

| 6.                                       | La sección CONFIGURATION                             | 25 |

| 7.                                       | La sección LIBRARY                                   | 27 |

| CAPÍ                                     | TULO III. DESCRIPCIÓN DE LA FUNCIONALIDAD            | 30 |

|                                          | Concepto de concurrencia.                            |    |

| 2.                                       | Estructura de un proceso                             |    |

| 3.                                       | Bloques de sentencias                                |    |

| 4.                                       | Asignaciones concurrentes                            |    |

| 5.                                       | La sentencia generate                                |    |

| ,                                        |                                                      |    |

|                                          | TULO IV. TIPOS DE DATOS Y SEÑALES                    |    |

| 1. Definición de tipos de datos.         |                                                      |    |

|                                          | 2. Tipo entero                                       |    |

|                                          | 3. Tipo matriz                                       |    |

|                                          | Definición de tipos compuestos                       |    |

|                                          | Tipos simples                                        |    |

| 6. I                                     | La librería IEEE                                     | 49 |

|                                          | TULO V. SUBSISTEMAS DIGITALES. EJEMPLOS DE DISEÑO    |    |

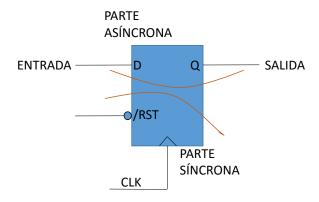

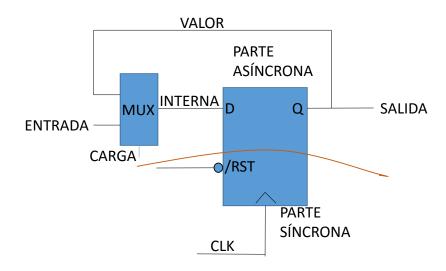

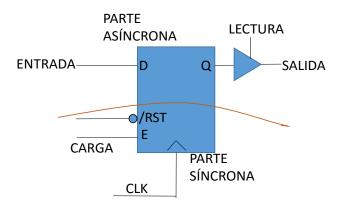

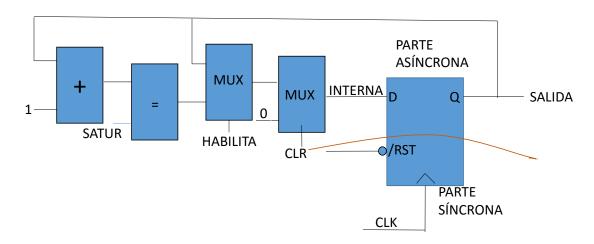

|                                          | 1. Codificación de Sistemas Síncronos                |    |

| 2. Codificación de sistemas aritméticos. |                                                      |    |

| 3. 0                                     | Codificación de módulos de memoria.                  | 67 |

| CAPÍ                                     | TULO VI. VHDL NO SINTETIZABLE. SIMULACIÓN Y MODELADO | 70 |

| Mecanismo de simulación.                 |                                                      |    |

| 2. \$                                    | Sentencias para modelado                             | 71 |

|                                          | 3. Construir un "Test Bench".                        |    |

|                                          | La librería TextIO                                   |    |

| CAPÍ                                     | TULO VII. BUENAS PRÁCTICAS CODIFICANDO EN VHDL       | 27 |

|                                          | Prácticas de codificación                            |    |

|                                          | 2 Tratamiento de la señal de reloj                   |    |

|                                          | Reglas para una síntesis segura                      |    |

|                                          | Facilitar la revisión de un código                   |    |

|                                          | HDL en estándares.                                   |    |

|                                          | oliografía                                           | 95 |

# CAPÍTULO I. LENGUAJES DE DESCRIPCIÓN DE HARDWARE

Este tema tiene por objeto dar una introducción general a los Lenguajes de Descripción de Hardware. Quiere aportar una visión de conjunto acerca del significado de en qué consiste diseñar grandes sistemas electrónicos digitales utilizando los HDL, y acerca de sus herramientas. Tras una breve introducción histórica se procede a analizar el salto cualitativo de diseñar con esquemáticos a diseñar en HDL. Posteriormente introduciremos el concepto de jerarquía de un diseño y de nivel de abstracción. Finalmente se describe en qué consiste una herramienta de síntesis de circuitos mediante HDL, elemento crucial en la nueva metodología para diseñar.

#### 1. Introducción histórica

La necesidad de construir circuitos digitales cada vez más complejos es patente día a día. Ya en el siglo XXI somos capaces de construir microprocesadores de muy altas prestaciones que están compuestos por millones de unidades funcionales (transistores) que realizan tareas de gran responsabilidad en la sociedad. Ingeniería aeroespacial, seguridad bancaria, automoción, identificación electrónica, gestión de recursos,...

En la práctica, el 100% de la electrónica de control y supervisión de los sistemas, elaboración de datos y transferencia de los mismos se realiza mediante circuitos integrados digitales, constituidos por una gran cantidad de transistores: son los llamados circuitos integrados de muy alta escala de integración, o VLSI.

Si en los años cincuenta y sesenta, en los albores de la electrónica integrada los circuitos eran esencialmente analógicos, en los que el número de elementos constituyentes de los circuitos no pasaba de la centena, en la actualidad el hombre dispone de tecnologías de integración capaces de producir circuitos integrados con millones de transistores a un coste no muy elevado, al alcance de una PYME. A mediados de los años sesenta Gordon E. Moore ya vaticinaba un desarrollo de la tecnología planar en el que cada año la escala de integración se doblaría, y de la misma manera aumentaría la capacidad de integrar funciones más complejas y la velocidad de procesamiento de esas funciones. Las predicciones de Moore se han cumplido con gran exactitud durante los siguientes 30 años, y que la tendencia continuará durante los próximos 20. En el año 2012 Intel esperaba integrar 1000 millones de transistores funcionando a 10GHz.

Si bien construir estos circuitos parece una cuestión madura, diseñarlos supone un serio problema. La microelectrónica digital continúa por el camino de la automatización, con herramientas específicas, como son los simuladores digitales o los generadores automáticos de layout, que resuelven el problema de la construcción del circuito y la verificación del mismo. Se utilizan, pues, fundamentos de la ingeniería de computación o CAE en las que se delegan en

herramientas software las tareas de manejo de grandes cantidades de información, bases de datos que, de forma óptima contienen la información acerca de la funcionalidad del circuito, de su geometría y de su conexiones así como de su comportamiento eléctrico. Si bien, por un lado la electrónica digital supone una simplificación funcional de un comportamiento analógico, con vistas a poder manejar grande volúmenes de información.

Con editores de esquemas somos capaces de dar una visión muy precisa y completa del diseño rápidamente, sin embargo esta metodología de captura queda circunscrita casi al mundo analógico.

Conforme al aumento de la complejidad de los circuitos digitales las prestaciones de los editores de esquemas no eran suficientes para responder a una capacidad de diseño tan elevada., que requiere una resolución explícita de los circuitos. Editar un esquema requiere, por tanto, un esfuerzo de desarrollo muy alto.

A principios de los años 90 Cadence Design Systems, líder mundial en sistemas de CAE para microelectrónica, propone el Verilog, un lenguaje alfanumérico para describir los circuitos de forma sencilla y precisa utilizando una sintaxis C: es el primer lenguaje de descripción de hardware en sentido amplio como veremos en epígrafes posteriores. Otros fabricantes de hardware habían propuesto un lenguaje más centrado en la resolución de un problema concreto: generación de una función para un dispositivo programable, resolución del circuito de una máquina de estados finitos a partir de su descripción de la evolución de los estados,... etc. Nacen los conceptos de descripción de alto nivel y de síntesis lógica, que posteriormente formalizaremos.

En el año 1982 el Departamento de Defensa de los Estados Unidos promueve un proyecto para desarrollar un lenguaje de descripción (conocido como MIL-STD-454L) de hardware que:

- Describiera los circuitos digitales de forma amplia: Funcionalidad, tecnología y conexionado

- Permitiera describir y verificar los circuitos a todos los niveles: funcional, arquitectural y tecnológico (posteriormente matizaremos estas tres categorías).

- Describiera la tecnología misma, para poder diseñar circuitos que sean independientes de la propia tecnología o bien durante la puesta a punto del proceso de fabricación.

- Describiera modelos del entorno en el que se va a insertar el circuito de forma que hubiese unas posibilidades de verificación más amplias del propio circuito.

El lenguaje resultante es el VHDL, que responde a las siglas VHSIC HDL (Very High Speed Integrated Circuits, Hardware Description Language), y es ratificado por el Instituto para la Ingeniería Eléctrica y Electrónica (IEEE, en 1987) en la norma IEEE-1076. Aunque en este sentido el Verilog cumple las propuestas anteriormente anunciadas, el VHDL se impone como

lenguaje estándar de diseño. Posteriormente veremos diferencias generales entre uno y otro. Por el momento nos referiremos a los HDL's como lenguajes alfanuméricos comprensibles para describir circuitos electrónicos en sentido amplio. En primer lugar veremos cuál ha sido la aportación de los HDL's en la metodología clásica de diseño.

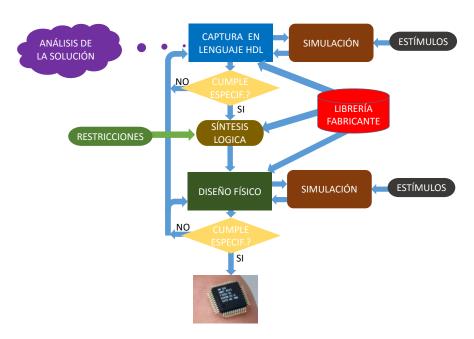

# ANÁLISIS DE LA SOLUCIÓN NO CUMPLE ESPECIF.? SI DISEÑO FÍSICO SIMULACIÓN ESTÍMULOS ESTÍMULOS ESTÍMULOS

# 2. Los HDL's en la metodología de diseño.

Ilustración 1. Metodología Clásica

# 2.1. Metodología clásica.

La secuencia de herramientas informáticas que procesan un diseño desde su descripción en un método fácilmente comprensible por el hombre hasta la información final, útil para la fabricación del dispositivo se llama *flujo de diseño*. La figura representa un flujo general que puede incluir más herramientas.

El proceso de elaboración de un diseño es un proceso de análisis jerárquico. Suelen ser diagramas de bloques y las señales que los conectan estableciendo las relaciones entre ellos. A su vez estos bloques son descompuestos en otros más simples, de menor rango en la jerarquía. Este proceso continúa hasta alcanzar funciones basadas en los elementos de menor entidad. A este proceso se le denomina descomposición *Arriba-Abajo* (Up-Bottom), usualmente realizado sin la ayuda de ninguna herramienta informática.

Terminada la etapa de decisiones, se procede a la introducción del diseño. Si utilizamos librerías de elementos básicos proporcionadas por los fabricantes (también llamados *primitivas*) construimos los primeros elementos de la jerarquía a partir de estas primitivas creando y verificando estas funciones del primer estadio jerárquico. Estos primeros bloques se incorporan a la librería de elementos que constituirán nuestro diseño.

Seguidamente construimos y verificamos el segundo nivel, tercero, cuarto, ... hasta llegar al nivel más elevado, que es nuestro diseño y las interconexiones con el sistema exterior. Esta es la fase de la metodología *Abajo-Arriba* (Bottom-Up). Cada unidad funcional es incorporada a la librería de diseño de forma que varias funciones podrían hacer uso de una misma función de inferior rango jerárquico. Este es el concepto denominado *reusabilidad* de una función.

#### 2.2. Metodología basada en HDL's

La introducción de los HDLs como métodos de descripción de circuitos han enriquecido el proceso de creación de un diseño, lo han acelerado y asegurado, abaratando los costes de desarrollo, o permitiendo abordar diseño más complejos.

La figura 2 muestra la modificación del flujo clásico cuando se utiliza esta técnica para la introducción del diseño. Existen varias mejoras sustanciales:

Ilustración 2. Metodología utilizando HDL

La librería de diseño es independiente de la tecnología para la que se diseña, por lo que la reusabilidad de los módulos constituyentes es total. No solo se puede compartir entre diseños sino que puede ser compartido por diferentes procesos de fabricación. Es independiente de la tecnología. El código introducido es de *Alto Nivel* y la simulación para su comprobación es asimismo de *Alto Nivel*. Solamente cuando se obtiene una imagen física del diseño puede predecirse con cierta certeza si cumple o no cumple las especificaciones. El programa de síntesis ha de alimentarse con el diseño, las condiciones de contorno en que funcionará, y la tecnología disponible del fabricante. El resultado será un código HDL de *Bajo Nivel* o lo que es lo mismo una representación del circuito alfanumérica compuesta por primitivas y sus conexiones, lo que se conoce como una *netlist*. Esta *netlist* se podría representar en un plano esquemático, pero no encontraríamos una ordenación racional y comprensible entre las primitivas y sus conexiones. Se utiliza como base de datos para alimentar el flujo de síntesis física.

La penalización ha sido la pérdida de cierto control en la generación del circuito, ya que en la nueva metodología hay una fase de *síntesis* automática en la que se cede a una herramienta software la responsabilidad de la resolución del circuito final. Nos acercamos a la situación ideal de la obtención totalmente automática del circuito a partir de las especificaciones.

En la práctica esta aproximación es la más utilizada en la que el diseñador ha cedido la responsabilidad de diseño de módulos regulares, sin la necesidad de verificar su correcta implementación. Por ejemplo un multiplicador editado en un esquema a base de puertas lógicas elementales (primitivas) había de ser verificado ante prácticamente todas las posibles combinaciones de las entradas. Mediante lenguajes de alto nivel la sentencia a\*b representa todo el circuito multiplicador correctamente generado automáticamente por un programa.

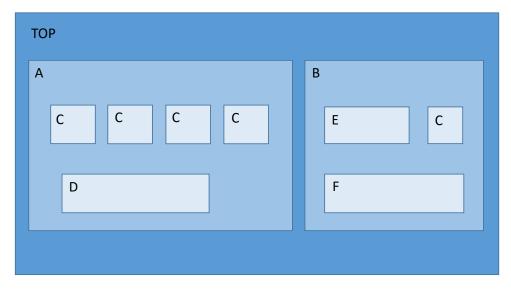

# 3. Jerarquía de un diseño.

En este estadio del desarrollo del tema es fácil comprender la idea de descomposición jerárquica de un diseño. Un diseño de gran dimensión, típico de un circuito microelectrónico digital requiere una buena organización del diseño, una descomposición razonada en módulos de inferior rango, que se suceden con una descripción cada vez más detallada de sus funciones, los llamados bloques funcionales. En realidad se sigue la conocida táctica de *divide y vencerás*.

Ilustración 3. Ejemplo de descomposición jerárquica

#### 4. Niveles de abstracción de un HDL

Como se ha comentado un HDL puede expresar un mismo diseño bajo diversos puntos de vista, son los llamados **niveles de abstracción**. El más elevado es una descripción en la que se define el comportamiento del circuito, es el llamado nivel **comportamental** (*behavioral*). El más bajo es un modelo íntimamente relacionado con la tecnología compuesto por primitivas y conexiones, representando la estructura del circuito, es el llamado nivel **estructural** (*structural*). También llamaremos nivel estructural al que expresa una interrelación entre bloques funcionales del mismo nivel jerárquico. Posteriormente veremos que podemos formar estructuras intermedios o **mixtos** compuestos por mezclas de ambos, en el que las unidades de un nivel estructural no son primitivas, sino que son módulos de rango jerárquico inferior.

#### 5. HDL: Programa o diseño.

El lector habrá notado que hemos procurado eludir la palabra "programa" a la hora de referirnos a la elaboración de un código HDL, ya que nos referiremos a él siempre como "diseño HDL". Como programa conocemos a una secuencia ordenada de comandos y funciones, que realizan unas tareas definidas en una computadora y la propia secuencia determina un comportamiento u otro. Estos comandos y funciones están expresados en un lenguaje alfanumérico que es fácilmente comprensible por el hombre, pero que tiene una proyección directa sobre el lenguaje comprensible por la computadora, y por tanto, fiel a su arquitectura. La traducción de uno a otro la realiza un programa compilador. .

Durante la ejecución del programa se procesan una tras otra las instrucciones secuencialmente condicionadas por la arquitectura de la Unidad Centra de Proceso (CPU). Cualquiera que sea su arquitectura, La estructura del programa toma por tanto la forma de una **secuencia** de instrucciones, accesos a memoria y saltos en flujo de ejecución.

Los lenguajes de descripción de hardware, HDLs, realizan aquello para lo que están diseñados, es decir, para describir un circuito o parte de un circuito hardware: Describen un comportamiento propio de un circuito en sentido amplio y por tanto no existen precedencia entre la activación de una parte del mismo u otra. Representan un comportamiento inherentemente **paralelo**. Esto tiene un conjunto de implicaciones que han de tenerse en cuenta a la hora de elaborar el diseño que particularizaremos al caso del VHDL. La primera implicación es la relación entre el lenguaje y la plataforma de desarrollo, que es una computadora y tiene el comportamiento descrito en el párrafo anterior. Por tanto simulación y síntesis han de estar provistas de mecanismos o artificios que <u>emulen</u> el paralelismo y que inciden directamente en la formulación del código. La segunda implicación es en un cambio de mentalidad en el diseñador a la hora de elaborar la descripción del diseño, estando habituado a realizar programas software. El mencionado ahorro en este caso exige une cuidadosa planificación del diseño previa a su elaboración. Existen usos típicos del programador de software que están absolutamente prohibidos en la formulación de un diseño hardware.

Un caso típico es utilizar variables auxiliares para almacenar temporalmente un valor. Posteriormente es posible reutilizar de nuevo la misma variable en otro punto del programa. Este uso es muy poco aconsejable si estamos diseñando circuitos, ya que una variable de este estilo sería un registro, con diferentes accesos y salidas, implicaría una compartición del mismo registro por varios módulo... en esencia algo poco recomendable. Sin embargo en un software es útil, ya que una variable así es una posición de memoria que puede accederse cuantas veces sea preciso y si se reutiliza el programa resultante es más compacto.

```

int aux;

....

aux=a+b;

...

c=función1(aux, ...);

...

aux=a*b; //reutilización de la variable

...

j=función2(aux, ...);

```

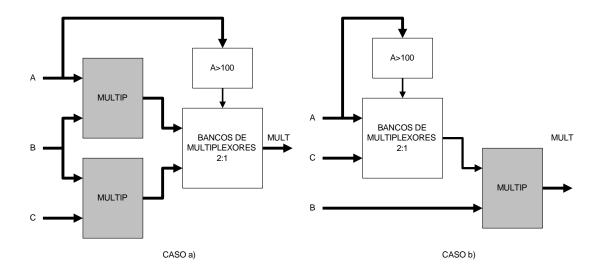

Otro caso muy corriente es la utilización de módulos aritméticos. En un diseño HDL, una suma o un producto implica necesariamente la síntesis de un circuito digital suma o producto. Cuando se declara la misma operación varias veces en software se utilizan el sumador y el multiplicador de la CPU exhaustivamente, sin más. En HDL el resultado sería un circuito con múltiples operadores que ocuparían gran cantidad de área de silicio. Es importante, por tanto, "ayudar" al programa de síntesis a elaborar el diseño definiendo una estructura que defina el circuito a nivel modular, lo que más adelante llamaremos diseño **rtl** (register transfer level), como nivel de abstracción adecuado para diseñar.

Otra situación muy típica es la evaluación secuencial de asignaciones:

a=a \* b;

El procesador evalúa a \* b y almacena el resultado en un registro propio, para posteriormente transferir el valor a la posición de a. Esto es algo impensable en hardware ya que se trata de describir un multiplicador cuya salida es la entrada, es decir, una realimentación combinacional.

Queda, pues, comentar el proceso que realiza una herramienta de síntesis a la hora de elaborar el circuito a partir de nuestra descripción del hardware:

- 1. Generación del código en un lenguaje paralelo, comprensible por el usuario (VHDL, Verilog, ABEL, ...).

- 2. Análisis sintáctico para detección de errores en la generación del código.

- 3. Elaboración del módulo, identificación y asignación de una imagen hardware del mismo (existen comandos y funciones de los HDL's que no son traducibles a hardware, y que se utilizan para la simulación), lo que se conoce como *modelo de referencia* de una estructura HDL.

- 4. A partir del modelo de referencia, se genera un circuito basado en primitivas.

- 5. Optimización del circuito, teniendo en cuenta las condiciones de contorno del diseño, es decir, generación automática del diseño final con las restricciones definidas por el usuario.

- 6. Elaboración de una descripción en bajo nivel del circuito, una *netlist* en un formato estándar para la síntesis física.

En los lenguajes HDL's se da la doble implicación, la de describir un hardware para implementación de un circuito (síntesis del circuito) y modelado del circuito (simulación del circuito), de la tecnología y del sistema. Por tanto existen funciones que no identifican bien un circuito. Por ejemplo, en VHDL se puede escribir el comando:

#### wait for 47ns;

¿existe un circuito capaz de hacer la operación de espera de 47ns exactos? Obviamente no. Sin embargo puede servir para expresar el retardo de una señal o un módulo en simulación. Distinguiremos pues, HDL para síntesis y HDL para modelado y simulación. El primero es un subconjunto del segundo.

# 6. Lenguajes HDL

Existen un buen número de lenguajes HDL's la mayoría de ellos con un propósito limitado. Los más conocidos son:

• ABEL: Lenguaje promovido por XILINX para la introducción de módulos de carácter específico, como máquinas de estados finitos.

- AHDL: Lenguaje en desuso promovido por ALTERA para facilitar la introducción de diseños en sus FPGA's. En la actualidad AHDL hace referencia a un HDL para diseño de circuitos analógicos.

- EDIF, XNF, ...: No son lenguajes propiamente dichos, en el sentido de no ser fácilmente comprensibles por el usuario, pero se utilizan cómo medios para transferir *netlist* entre herramientas.

#### 6.1 VHDL

El VHDL fue desarrollado por la Departamento de Defensa de los Estados Unidos para modelar y simular sistemas. Emula el paralelismo mediante eventos y utiliza como modelo de formulación el ADA. El Instituto para la Ingeniería Eléctrica y Electrónica (IEEE) ha formulado una norma que regula el VHDL: la norma IEEE 1076-1987.

# 6.2 Verilog

Es un lenguaje HDL propiedad de CADENCE Design Systems, fabricante de software para diseño de circuitos integrados, de la misma manera emula el paralelismo mediante eventos. Sigue la sintaxis del C.

# 6.3 VHDL vs Verilog

Llevamos casi un década debatiendo cuál de los dos lenguajes es el más apropiado para diseñar. La comunidad científica ha llegado a la conclusión de que no existe una razón de peso para claramente decantarse por uno o por otro. Por un lado, Verilog nace ante la necesidad de mejorar un flujo de diseño y por tanto es un lenguaje que cubre todas las necesidades de diseño y simulación. El resultado es un lenguaje simple y flexible que es fácil de aprender. Por otro, VHDL es un lenguaje más rígido y con una sistematización en el código que lo hace más legible, aunque las reglas de diseño obligan a proceder de forma, a veces poco ágil. Ante la duda de cuál de ellos enseñar en este curso la respuesta está en la propia comunidad científica: lo ideal es conocer ambos. En este sentido se coincide que el conocedor de Verilog le cuesta aprender VHDL, sin embargo el proceso contrario es en general, más aceptado. El programador de VHDL aprende Verilog en poco tiempo La experiencia de los autores de estos capítulos es precisamente esa, y que conceptualmente es más didáctico el VHDL.

# 6.4 Nuevos lenguajes de alto nivel

A partir de los años 2000 han nacido nuevos lenguajes de alto nivel cuya sintaxis y método de codificación son idénticos a los lenguajes informáticos más usuales en ingeniería como el C ó C++. Estos lenguajes tienen como objeto facilitar la traslación de los lenguajes de diseño y pruebas de estudio a la descripción hardware. Los más conocidos son Handel-C de Celóxica y SystemC.

Incluso se ha introducido lenguajes de muy alto nivel basados en bloque funcionales. Dado que el coste por puerta lógica ha decrecido, sugieren que no es tan importante la implementación final del código, y por tanto el buen estilo de programación, como que haga la implementación respetando la funcionalidad. Esos lenguajes de muy alto nivel utilzn herramientas como Simulink como captura algorítmica, pero exceden en mucho lo objetivos de este documento,

# 7. Síntesis de Circuitos.

Hemos mencionado repetidamente la palabra <u>síntesis</u> como un proceso fundamental en la generación del circuito. En el año 1987 A. Sangiovanni-Vincetelli, uno de los mayores contribuidores al CAD/CAE para circuitos VLSI definía síntesis como "generar el circuito desde una descripción algorítmica, funcional o de comportamiento del circuito, una descripción de la

tecnología y una descripción de las condiciones de diseño en una función de costes. El resultado ha de obtenerse en un tiempo razonable de computación y con la calidad similar o mejor a la que el razonamiento humano podría obtener". La síntesis completa de un circuito requiere tres niveles:

- 1. Síntesis modular o particionamiento razonado: es el análisis a nivel de diseño. Esta labor se la hemos dejado al diseñador.

- 2. Síntesis lógica, combinacional, secuencial, algorítmica y de comportamiento.

- 3. Síntesis física. Es decir, generación automática del layout, de la tarjeta PCB, de la programación de la FPGA,...

El tema que nos ocupa se centra fundamentalmente en el punto segundo. La naturaleza del problema estriba en que no existe una única formulación para una misma función lógica, es decir, una misma función puede adoptar muchas expresiones, y su implementación y comportamiento físico es diferente en cada caso. En particular existen dos casos especialmente interesantes: aquel en que el área ocupada por la función es mínima y aquel en que el número de etapas o niveles de la función es mínimo, ya que hay una relación directa entre el número de etapas y el retardo en la propagación de las señales. Debido a que son dos factores normalmente contrapuestos, en cada caso ha de evaluarse la formulación más adecuada o bien una situación intermedia, solución que está definida por las condiciones de diseño. En adelante síntesis será un sinónimo de síntesis lógica.

Durante los años 80 y 90 las investigaciones en materia de síntesis se han centrado en desarrollar algoritmos que resuelven de una manera eficiente y óptima diferentes estructuras típicas de los circuitos digitales. Podemos identificar:

- Síntesis a dos niveles y síntesis multinivel. Optimización de funciones combinacionales.

- Síntesis de módulos aritméticos. Generación de estructuras regulares que permitan generar circuitos digitales aritméticos de cualquier dimensión.

- Síntesis de circuitos secuenciales: FSM's, Memorias, Contadores, Registros,...

Por tanto se han desarrollado algoritmos específicos para cada estructura y estrategias diferentes para cada tipo de módulo a implementar, por tanto en el proceso de síntesis lógica ha de haber una etapa previa de identificación del módulo en cuestión. Un programa de síntesis es, por tanto, una recopilación de programas específicos de optimización, aplicados a cada estructura digital, sucedido de una optimización combinacional global. De ahí que en el punto 5 de este capítulo descrito la necesidad de obtener un modelo de referencia como paso previo a la síntesis del circuito.

Comercialmente existen varios programas de síntesis en el mercado que merecen mencionarse:

- SYNOPSYS, programa de carácter general que permite realizar síntesis ante multitud de lenguajes y tecnologías. Funciona sobre plataforma UNIX.

- Leapfrog, de CADENCE para VHDL

- VerilogXL, de CADENCE para Verilog.

- Leonardo de MENTOR GRAPHIC's, multilenguaje en plataforma PC

- FPGA-EXPRESS, de Synopsys para PC y centrado en FPGA's. (Obsoleto)

- Sinplify , también de Synopsys

ISE y Vivado, de Xilinx o Quartus de ALTERA

# CAPÍTULO II. ESTRUCTURA DE UN BLOQUE FUNCIONAL EN VHDL

# 1. Cuestiones previas

Una vez introducida la necesidad de diseñar utilizando lenguajes HDL y todo lo que ello significa nos decantamos por presentar el VHDL como lenguaje de diseño. Existen varias cuestiones previas que hay comentar antes de iniciar la exposición formal del lenguaje.

Primeramente, el VHDL es un lenguaje en el que se define el sentido del flujo de las señales, es decir, una señal es de entrada y/o salida definida en el código, no por la evolución de la señal en si misma. La importancia de este comentario radica en que el nivel de descripción más bajo que podemos alcanzar en VHDL es el nivel de puerta lógica, y no de transistor. Por ejemplo, para representar un *switch* en VHDL se ha de incluir una subrutina de cerca de 750 líneas de código, inefienciente a todas luces. En Verilog esto esta bien resuelto por comando *switch*.

En segundo lugar, el VHDL no es sensible a mayúsculas y minúsculas, por tanto la señal PEPE es igual a la señal PePe y a su vez a la señal pepe.

Los comentarios son solamente de línea y van marcados por dos signos menos:

--Esto es un comentario en VHDL

El lenguaje VHDL está dotado de muy pocos recursos inicialmente, de pocas funciones y tipos de variables. Para darle mayor versatilidad es preciso utilizar librerías estándar que le dotan de mucha mayor potencia para representar comportamientos digitales. Dejaremos a capítulos posteriores la formalización de esta idea.

El mecanismo para realizar la síntesis de un *diseño* descrito en VHDL se realiza, de modo estándar utilizando una librería de compilación donde se ubican los modelos de referencia, que físicamente es un subdirectorio en el directorio de diseño. Esta librería de modelos, por defecto se suele llamar WORK. Ampliaremos esta idea en el apartado referido a librerías.

# 2. Un primer ejemplo en VHDL

En esta sección vamos a exponer un ejemplo de las diferentes posibilidades del lenguaje VHDL. En particular escribiremos el código que describe un multiplexor 4 a 1, de tal manera que se pongan de manifiesto los diferentes elementos fundamentales del lenguaje. Estos elementos serán debidamente formalizados en secciones posteriores. El multiplexor tiene un bus de entradas de 4 bits llamado *datos* y un bus de selección de dos bits, llamado *selector*. La salida es la señal *salida*. Además estamos interesados en dar la misma descripción desde diferentes puntos de vista.

En primer lugar haremos la descripción basada en la función lógica del multiplexor, que corresponde a una arquitectura de tipo *comportamental* (behavioural)

Esta es una descripción de comportamiento, pero basada en la resolución de la lógica asociada a nuestro multiplexor. El programa de síntesis realmente lo que hace es revisar las funciones y generar un circuito equivalente eliminando redundancias si las hubiere, o buscando la morfología de área mínima, consumo mínimo ó mínimo retardo, dependiendo de las restricciones impuestas al proceso de optimización lógica.

Una segunda versión del multiplexor puede realizarse empleando sentencias de más alto nivel, en la que se describe su comportamiento mediante recursos del lenguaje más cecanos al pensamiento humano. En particular utilizaremos la sentencia WHEN condición ELSE, que expresa una asignación bajo el cumplimiento de una condición y su alternativa:

```

END mux41;

```

**END** comport2;

```

ARCHITECTURE comport2 OF mux41 IS

BEGIN

Salida <= datos(0) WHEN (selector(0)='0' AND selector(1)='0') ELSE

datos(1) WHEN (selector(0)='1' AND selector(1)='0') ELSE

datos(2) WHEN (selector(0)='0' AND selector(1)='1') ELSE

datos(3);

```

En esta formulación se utiliza un procedimiento más complejo de asignación y no es inmediata su implementación en un circuito. En particular, para la satisfacción de la asignación de datos(3) debe cumplirse la no asignación de las condiciones anteriores, dicho de otra manera, el código expresa una precedencia de datos(0) frente a los demás. Cuando se formula directamente el circuito que lo representa, en buena lógica los datos(0) tiene un menor tiempo de propagación que el resto a través del circuito. La fase de optimización posterior ecualiza los retardo al eliminar las redundancias que hay implícitas.

Una versión alternativa sería:

Es este caso en la fase de optimización se realizaría menos esfuerzo, ya que la estructura es más parecida a la versión final. Un ejemplo para controlar la estructura del multiplexor es el siguiente:

```

ARCHITECTURE compor4 OF mux41 IS

BEGIN

Salida <= datos(0) WHEN (selector(0)='0' AND selector(1)='0') ELSE 'Z';

Salida <= datos(1) WHEN (selector(0)='1' AND selector(1)='0') ELSE 'Z';

Salida <= datos(2) WHEN (selector(0)='0' AND selector(1)='1') ELSE 'Z';

Salida <= datos(3) WHEN (selector(0)='0' AND selector(1)='1') ELSE 'Z';

END comport4;

```

En este caso el circuito se realiza con una estructura muy distinta de las anteriores, basada en puertas triestado. Esta situación típica cuando los multiplexores son de gran tamaño, ya que se vierte sobre el conexionado la función OR del multiplexor. El esfuerzo de optimización se centra en el decodificador del multiplexor.

Finalmente haremos una versión estructural del multiplexor. Para ello supondremos que ya existe una descripción de un multiplexor más simple 2 a 1, descrito bajo la entidad mux21. En este caso obviamos su arquitectura, ya que solamente estamos interesados en su descripción como entidad.

En ésta versión haremos tres instancias del mux21. Además se precisa la utilización de señales auxiliares internas, llamadas *salida\_parcial*. Como se puede comprobar, es la utilización de una descripción puramente conectiva.

```

LIBRARY IEEE;

USE IEEE. Std_logic_1164.all;

ENTITY mux41 IS

PORT(

datos: IN std_logic_vector(3 downto 0);

selector: IN std_logic_vector(1 downto 0);

salida: OUT std_logic

);

END mux41;

ARCHITECTURE estruct OF mux41 IS

COMPONENT mux21

PORT(

datos: IN std_logic_vector(1 downto 0);

selector: IN std logic;

salida: OUT std logic

END COMPONENT;

```

```

SIGNAL salida_parcial: std_logic_vector(1 downto 0);

BEGIN

mx1: mux21

PORT MAP(datos =>datos(1 downto 0), selector=>selector(0), salida=>salida_parcial(0));

mx2: mux21

PORT MAP(datos =>datos(3 downto 2), selector=>selector(0), salida=> salida_parcial(1));

mx3: mux21

PORT MAP(datos => salida_parcial, selector=> selector(1), salida=>salida);

END estruct:

```

Esta es la situación que eventualmente se obtendría tras un proceso de optimización en el caso de que mux21 fuera un componente *primitiva*, aunque en este caso somos nosotros los que hemos definido la estructura.

#### 3. Estructura de un diseño VHDL

Una de las grandes aportaciones de los lenguajes HDL, como se expuso en el capítulo 1, es la posibilidad de organizar jerárquicamente los diseños, de tal manera que cada elemento, junto con los elementos de inferior nivel jerárquico, es en sí mismo un diseño autocontenido. En consecuencia cada unidad en la jerarquía tiene entidad como circuito, con entradas, salidas y funciones.

La unidad jerárquica en cuestión es designada por la palabra reservada entity o entidad. La entidad tiene asociado un nombre identificador usualmente relativo a la función que realiza. Cada vez que hagamos uso de este circuito utilizaremos el nombre asociado. Una entidad es modelo de una unidad funcional hardware que puede representar un sistema completo, un subsistema, una tarjeta, un chip, una macro-célula, una puerta lógica o cualquier nivel de abstracción de ellos. Asimismo está definida por señales de enlace con el exterior y una arquitectura funcional.

El VHDL ha previsto la posibilidad de modelar diferentes arquitecturas para una misma entidad de ahí que haya que asignar nombres tanto a la entidad como a la arquitectura. Asimismo dispone de un mecanismo para poder acceder de forma automática a las diferentes arquitecturas de una misma entidad desde una entidad de orden jerárquico superior. Es el mecanismo de la configuración o **configuration**

# 3.1 Código general de una entidad VHDL

El código de una entidad se presenta en el siguiente esquema:

```

--Zona de declaración de librerías

LIBRARY nombre_librería;

USE paquete_funciones_librería.all;

--Cabecera de la entidad

ENTITY nombre_entity IS

GENERIC(.....);

PORT(.....);

CONSTANT señal : tipo :=valor;

CONSTANT señal : tipo :=valor;

END nombre_entity;

--Cuerpo de la entidad

ARCHITECTURE nombre_architecture OF nombre_entity IS

--Declaración de sub-entidades (componentes) y señales internas

BEGIN

--Descripción de la funcionalidad

END nombre_architecture;

--Enlace con las arquitecturas de otras entidades

CONFIGURATION nombre_configuracion OF nombre_entidad IS

FOR nombre_arquitectura

--Cuerpo de la configuración

END nombre_configuracion;

```

El desarrollo de este tema consiste en explicar cada uno de los elementos expuestos en el esquema anterior.

# 4. La sección ENTITY

Una declaración entidad representa una interfaz entre la funcionalidad que representa y su entorno. Identifica la unidad funcional dentro de una jerarquía de forma unívoca. No pueden existir dos entidades del mismo nombre en la jerarquía definidas con un interfaz diferente. Junto con la palabra ENTITY hay asociados dos campos:

- GENERIC: utilizado para pasar parámetros a la entity

- PORT: utilizado para definir las señales que relacionan la entity con el resto del diseño. Veamos un ejemplo concreto:

#### **ENTITY** contador IS

```

GENERIC(SATURAC: integer:= 1000; N:integer:=10);

PORT(

CLK: in BIT;

RST: in BIT;

ENABLE: in BIT;

COUNT: out BIT_VECTOR(N-1 DOWNTO 0);

SATUR: out BIT

);

END contador;

```

El código representa una descripción de las entradas y salidas de un contador de tamaño 10. La gran ventaja es que es posible redefinir los parámetros SATURAC y N tantas veces como queramos y extender el contador a la longitud y al valor de saturación que convenga en cada momento sin modificar el código. Cada vez que se utiliza la entidad como parte del diseño se pueden determinar los parámetros que definitivamente definen el diseño. Sin embargo hemos dado —obligatoriamente- un valor por defecto, tanto a SATURAC, 1000, como a N, el valor 10 al tamaño del contador. El motivo es doble. Por un lado el valor por defecto se utilizará en caso de no reasignación del valor del parámetro, pero la más importante es que los parámetros tienen la misión de dar coherencia al modelo del circuito, es decir, un contador de tamaño N y SATURAC no tienen sentido como circuito, sin embargo, al dar un valor sí quedan bien definidos y a la hora de generar su correspondiente modelo hardware de referencia se facilita generar la arquitectura. Los parámetros se utilizan para controlar características estructurales, de flujo de datos o comportamentales de una entidad, o simplemente como documentación. Pueden definirse tantos parámetros como se desee. De los tipos posibles de parámetros hablaremos en el capítulo siguiente. La sintaxis seguida es:

Nombre\_parámetro : tipo\_parámetro := valor\_por\_defecto;

La cláusula PORT indica las señales que interrelacionan la **entity** con el resto del diseño. La sintaxis es:

Nombre\_señal: dirección tipo\_de\_señal;

El nombre de la señal identifica unívocamente la señal en cuestión. No puede haber otra señal dentro de la arquitectura con el nombre de la señal. El campo "dirección" de la señal indica el sentido del flujo de la misma. Este campo puede tomar los siguientes valores:

- IN para indicar que la señal es una entrada

- OUT para indicar que la señal es una salida

- INOUT para indicar que la señal es una entrada o salida dependiendo de cada instante.

- BUFFER tipo extendido de salida.

- LINKAGE es un tipo enlace genérico de salida que está en desuso. La norma vaticina su desaparición.

Una señal IN recibe sus valores desde el exterior de la entidad. Por tanto, no puede ser reasignada en el interior de la entidad, es decir no puede aparecer a la izquierda de una asignación en la arquitectura:

Una señal OUT genera valores al exterior de la entidad. No puede ser asignada a ninguna otra señal en la arquitectura:

```

A<=Señal_out; --Error

Señal_out<=A; --Correcto

```

Una señal INOUT puede ser asignada en ambos sentidos y es responsabilidad del diseñador determinar en qué condiciones de la función lógica descrita la señal puede ser IN o OUT.

El lector podría pensar que para evitar errores lo más sencillo sería describir todas las señales como INOUT. Sin embargo esto sería atentar contra la naturaleza de los HDL, que es describir de la forma más explícita y precisa posible un circuito. De la otra manera un mal estilo de diseño nos llevaría a una mala descripción del circuito y seguramente a otro tipo de errores.

Una señal BUFFER es señal de salida directamente asignable a otra señal dentro de la arquitectura, pero no puede ser forzada desde el exterior, dicho de otra manera, no es en ningún momento una entrada. Se utilizan fundamentalmente para describir señales que realimentan dentro de la entidad y simultáneamente salen al exterior. Un caso típico es un contador síncrono. Sin embargo en la práctica hay sintetizadores que utilizan la palabra BUFFER para forzar un cierto comportamiento eléctrico de una señal. Por tanto hay sintetizadores que no lo contemplan,

La declaración de tipos **constant** tiene por objeto de la definición de elementos de valor constante dentro de la entidad. Es posible su reasignación tras la declaración como instancia de la entidad.

No entraremos en detalles acerca de los tipos de datos, cuestión que se abordará en el capítulo correspondiente.

5. La sección ARCHITECTURE

La arquitectura de la entidad es la descripción de la funcionalidad. Consta de dos partes:

La parte declarativa, donde entre otros, se especifican los elementos de tipo estructural que van a componer la arquitectura, es decir:

• Nuevos tipos de señales subtipos y constantes.

• Señales internas. Son enlaces entre los diferentes elementos que definen la arquitectura.

• Entidades de orden inferior en la jerarquía, llamadas componentes o component.

• Funciones, bloques, grupos,...

La parte descriptiva, donde se define la funcionalidad que concretamente se le asigna a la arquitectura. De las órdenes comandos y funciones que se pueden incluir en una arquitectura hablaremos más adelante. Por ahora profundizaremos en la cuestión de la jerarquía de un diseño y cómo se especifica en una arquitectura.

5.1 Diseño jerárquico (estructural) en una arquitectura.

En primer lugar especificamos en la parte declarativa qué componentes (**component**) se utilizarán en la arquitectura. Hacemos referencia a otras entidades, a sus señales de enlace y a los parámetros.

Luego se especifican las señales mediante la palabra **signal**, seguida de uno o varios nombres y de un tipo según la sintaxis:

**SIGNAL** nombre1, nombre2, ...: *Tipo de señal*:= *valor inicial*;

Todas las señales especificadas pertenecen al mismo tipo. Como se puede apreciar este es el mismo esquema empleado en la declaración de las señales de enlace de la entidad, con la salvedad de omitir la direccionalidad de la señal. Asimismo, y opcionalmente se puede asignar un valor inicial de la señal. Este valor suele utilizarse en simulación y es omitido por los sintetizadores.

También se pueden declarar valores constantes:

**CONSTANT** nombre: *Tipo de señal*:= *valor inicial*;

Veamos un ejemplo concreto. Utilizando la declaración de la entidad superior construiremos una arquitectura que llama dos veces al contador anterior. Supongamos un contador doble:

```

ENTITY doble contador IS

PORT(

clk,rst,enable1,clr: IN BIT;

salida: OUT BIT;

cuenta: OUT BIT_VECTOR(7 DOWNTO 0)

);

END doble_contador;

ARCHITECTURE estructura_mod OF doble_contador IS

COMPONENT contador

GENERIC(N:integer:=10);

PORT(

CLK: in BIT;

RST: in BIT:

CLEAR: in BIT;

ENABLE: in BIT;

COUNT: out BIT_VECTOR(N-1 DOWNTO 0);

SATUR: out BIT

END COMPONENT;

SIGNAL enlace1, slogico0: BIT;

SIGNAL cuenta1: BIT VECTOR(7 DOWNTO 0);

BEGIN

slogic0 \le 0';

cont1: contador

GENERIC MAP(N=>8)

PORT MAP(CLK=>clk, RST=>rst, CLEAR=> CLR, ENABLE=>enable1,

COUNT=>cuenta1, SATUR=>enlace1);

cont2: contador

GENERIC MAP(N=>12)

PORT MAP(CLK=>clk,RST=>rst, CLEAR=>slogic0, ENABLE=>enlace1,

COUNT=>OPEN,SATUR=>salida);

END estructura mod;

```

El ejemplo muestra la utilización de un mismo componente varias veces. Lo primero que hay que haces notar es la presencia de una etiqueta que identifica cada uno de los componentes de una manera unívoca. cont1 y cont2 son dos instancias de una misma entidad *contador*, y cada uno de ellos tiene un valor diferente del parámetro. De ahora en adelante esta etiqueta, *nombre\_instancia*, identificará al componente. La sintaxis es simple:

```

nombre_instancia : nombre_entidad GENERIC MAP(.....)

PORT MAP(.....);

```

En segundo lugar debemos destacar la manera de referenciar señales internas a la entidad. Tras la declaración de los componentes se declaran señales que son interiores al diseño. En el ejemplo aparece la señal *enlace1* como señal interna, común a ambos bloques:

en un caso enlace1 es de salida y en el otro, de entrada. Obviamente en la declaración de la misma no existe direccionalidad, a diferencia de la señales de los puertos de la entidad.

En tercer lugar conviene repasar la sintaxis y la puntuación. La etiqueta de instancia va seguida del nombre de la entidad, en este caso el componente que se trata. Las secciones **generic** y **port** son ahora **generic map** y **port map**, indicando las señales que van a ser asociadas a sus entradas y salidas. En el caso de que hubiese direccionalidad en las señales, es decir, que vengan declaradas desde la entidad (en el ejemplo *clk*, *rst*, *enable1*, *salida*,...) la señal ha de conservar el tipo. Las cláusulas *map* no van separadas por ';'.

Finalmente la manera de asociar señales que se propone es especificando qué señal se asocia a qué entrada, mediante los caracteres '=>' y separados por comas. Este método se denomina pasar parámetros por **referencia**. En este sentido conviene hacer algún comentario adicional. Es correcto pasar los parámetros por **orden**, es decir con la sintaxis:

```

cont2: contador

GENERIC MAP(12)

PORT MAP(clk,rst,enlace1,OPEN,salida);

```

Si bien es más conciso, es también poco práctico, ya que un error obliga a estar constantemente comparando con el componente y verificando una correcta asociación, es decir, muy poco legible. La experiencia demuestra que siendo más explícito, si bien se escribe más, se tarda en tener éxito mucho menos tiempo. En este caso es obligado que aparezcan todos los parámetros.

#### La palabra reservada **open**.

La palabra reservada **open** se utiliza para dejar señales sin conectar. La omisión de un parámetro es equivalente a la asociación de **open**.

Es posible asociar **open** a una entrada, que es tanto como decir que se deja sin conectar, lo cual en la práctica no es nada aconsejable, ya que se deja libertad al proceso de síntesis para que realice las operaciones sin nuestro control. En la práctica se debe asociar un valor lógico concreto a la entrada para evitar resultados impredecibles. En VHDL no se admite que en la referencia a un componente se asocie un valor lógico directamente, por lo que hay que declarar una señal auxiliar.

```

constant clogic0: std_logic :='0'; --Este valor no se puede asignar

signal slogic0: std_logic; --Este es el modo de asignación

....

slogic0<='0';

....

port map (clr=> slogic0,....)

```

La asociación para la conexión de componentes se realiza mediante señales del mismo tipo por tanto no es válido asociar constantes con señales de puertos, de ahí que la asociación de *clogicO* no sería válida.

La arquitectura presentada es un ejemplo de arquitectura estructural, ya que está compuesta únicamente de componentes y sus enlaces. Si hacemos referencia al paralelismo entre ellos, este caso es un ejemplo claro que no existe precedencia en el comportamiento de un contador u otro, ya que ambos se activan de igual manera, aunque el segundo dependa del primero.

5.2 Diseño de comportamiento en una arquitectura.

En el nivel más bajo del diseño ha de haber una información acerca de la funcionalidad del propio diseño. No se hacen referencia a otros componentes, sino que en la propia arquitectura se definen las operaciones que se realizan sobre las señales. Sin entrar excesivamente en detalles, ya que serán motivos de capítulos posteriores.

5.3 Diseño con primitivas.

Las primitivas son las unidades funcionales elementales que describen el diseño después de realizar la síntesis. Están asociadas a la tecnología elegida y están representadas como componentes en una librería que el fabricante de circuitos integrados proporciona. Es posible realizar una descripción de un diseño a partir de una descripción mediante primitivas, lo que equivale a realizar un esquemático escrito.

# 6. La sección CONFIGURATION

La sección CONFIGURATION responde a un complejo mecanismo de selección entre las diferentes arquitecturas posibles de una misma entidad utilizada en un nivel jerárquico superior. Una configuración está asociada a una entidad y una arquitectura. Por tanto, mediante la selección de la configuración determinaremos qué arquitectura es seleccionada para esa entidad. Podemos definir tantas configuraciones como sean necesarias, ya que a ella se le asocia un nombre.

La sintaxis es:

CONFIGURATION nombre\_configuracion OF nombre\_entidad IS

**FOR** nombre\_arquitectura

FOR nombre instancia:

END FOR;

\_\_\_\_

END FOR;

**END** nombre\_configuracion;

Es en el nivel jerárquico inmediatamente superior donde se particulariza qué configuración se desea para determinada entidad. Veamos un ejemplo:

```

-- Entidad inferior

ENTITY mi_contador IS

PORT(

clk,rst,enable: in std_logic;

cuenta: out std_logic_vector(7 downto 0)

);

END contador;

--definimos dos arquitecturas diferentes para la misma entidad

ARCHITECTURE comport OF contador IS

BEGIN

END comport;

ARCHITECTURE estruct OF contador IS

BEGIN

END estruct:

--asociamos una configuración a cada una de las arquitecturas

CONFIGURATION comport_conf OF contador IS

FOR comport

END FOR;

END comport_conf;

CONFIGURATION estruct_conf OF contador IS

FOR estruct

END FOR;

END estruct conf;

-- configuración de la entidad superior que referencia el componente

CONFIGURATION estruct_top OF top IS

FOR estruct

FOR cont1: contador USE CONFIGURATION WORK.estruct_conf;

END FOR;

FOR cont2: contador USE CONFIGURATION WORK.comport_conf;

END FOR;

END FOR:

END estruct_conf;

```

En este ejemplo hemos utilizado dos arquitecturas diferentes del mismo componente. En el caso de que no exista la necesidad de variar las configuraciones se puede resumir en la cláusula ALL:

```

-- configuración de la entidad superior que referencia el componente

CONFIGURATION estruct_top OF top IS

FOR estruct

FOR ALL: contador USE CONFIGURATION WORK.estruct_conf;

END FOR;

END FOR;

END estruct_conf;

```

# 6.1 Estilo par entidad-arquitectura

Existe una sintaxis alternativa que permite una asociación más explícita:

```

CONFIGURATION estruct_top OF top IS

FOR estruct

FOR cont1: contador USE ENTITY WORK.contador(estruct);

END FOR;

FOR OTHERS: contador USE ENTITY WORK.contador(comport);

END FOR;

END FOR;

END ESTRUCT CONT;

```

En este caso hemos introducido también la cláusula OTHERS para identificar a aquello que no se ha hecho referencia previamente. Este primer ejemplo de una palabra que es muy

En la práctica este potente mecanismo es poco utilizado, dado que no se ofrecen muchas situaciones de varias arquitecturas para una misma entidad. Si solamente existe una única arquitectura en todos y cada uno de los componentes del diseño, la configuración será única y por tanto se omite la sección de configuraciones.

#### 7. La sección LIBRARY

utilizada en VHDL.

Tiene un especial interés el dedicar un párrafo completo a las librerías en VHDL, dado que en la práctica todas las extensiones del lenguaje se realizan utilizando este potentísimo mecanismo.

Mediante bibliotecas podemos definir componentes, funciones y procedimientos, es decir, unidades del lenguaje que pueden ser útiles en múltiples aplicaciones, siendo un elemento de reutilización del lenguaje. De esta manera, un componente de una librería ya analizada y sintetizada puede ser llamada en un código sin necesidad de tener que volver a declararlo como componente. Las librerías se estructuran en paquetes (packages) que permiten una fácil clasificación de los elementos que las componen.

La declaración de una librería sigue la siguiente sintaxis:

```

library MiLibreria;

use MiLibreria.Paquete1.all;

use MiLibreria.Paquete2.all; --Enmascara las funciones de Paquete1

```

De esta manera quedan accesibles todos (all) los elementos del *Paquete1* y *Paquete2* de la librería *MiLibreria*. En el capítulo seis nos dedicaremos en detalle a definir, declarar y construir nuestras librerías. Sin embargo nos detendremos en explicar algunos aspectos importantes de las librerías más utilizadas. Solo dos palabras para comentar que las funciones VHDL disponen del **mecanismo de sobrecarga** en sus llamadas, de forma que no solo se atiende a la

coincidencia del nombre de la función en la llamada, sino que además se verifica la coincidencia de los tipos de argumento de las mismas.

Finalmente, la presencia de funciones con igual nombre y tipo de argumentos en *Paquete1* y *Paquete2* hace que las funciones del primero queden enmascaradas por las del segundo, de ahí que si se desea utilizar parcialmente una de ellas, bien debemos cuidar el orden de declaración o bien sustituir la palabra **all** por las funciones que nos interesen.

#### 7.1 La necesidad de la librería *std\_logic\_1164*

El VHDL posee un limitado número de tipos y funciones que resultan insuficientes a la hora de describir completamente el comportamiento de un circuito digital. Por tanto se hace preciso que la extensión del lenguaje contemple un número más amplio de situaciones. En particular, los tipos de datos que maneja el VHDL de modo natural se reflejan en la siguiente tabla:

- **BIT**, {0,1}

- **BOOLEAN**, {false, true}

- CHARACTER, {la tabla ASCII desde 0 a 127}

- **INTEGER**, {-2147483647, 2147483647}

- NATURAL, {0, 2147483647}

- **POSITIVE**, {1, 2147483647}

- **STRING**, array {POSITIVE range <>} de CHARACTER

- BIT\_VECTOR, array {NATURAL range <>}de BIT

- Tipos físicos, como **TIME**

- **REAL**, {-1E38, 1E28}

- **POINTER**, para accesos indirectos a datos.

- FILE, para accesos a ficheros y pilas de datos del disco duro.

Ni que decir tiene que muchos de ellos corresponden a estructuras del lenguaje que no son sintetizables. De hecho, durante la síntesis de bloques VHDL casi nunca se utilizan de manera explícita y completa estos tipos de datos. Por tanto el VHDL de forma sistemática ha de extenderse mediante tipo de datos que presentan un campo de variabilidad mucho más cercano al funcionamiento eléctrico de un circuito. Se trata del paquete  $std\_logic\_1164$  de la librería IEEE. Normalmente esta librería aparece dando sentido a un nuevo tipo de datos, el  $std\_logic$ , que es un tipo enumerado y resuelto. Los detalles acerca de este tipo de datos se exponen en el capítulo cuarto de estos apuntes.

La cabecera de librerías estándar es típicamente:

#### library IEEE;

# use IEEE.std\_logic\_1164.all;

En esta librería se introducen los nuevos operadores relacionales asociados al nuevo tipo de datos.

# 7.2 Librerías aritméticas

El VHDL no tiene definidos de modo estándar operaciones aritméticas que permitan el uso de operadores. Es preciso, pues, la inclusión de librerías que faciliten la inclusión de operadores de tipo aritmético. La librería estándar para este caso es la *numeric\_std*. En el capítulo dedicado a comentar la utilización de las funciones aritméticas desarrollaremos las referencias a esta librería. Se estudiará a fondo en los capítulos cuatro y cinco.

# CAPÍTULO III. DESCRIPCIÓN DE LA FUNCIONALIDAD

#### 1. Concepto de concurrencia.

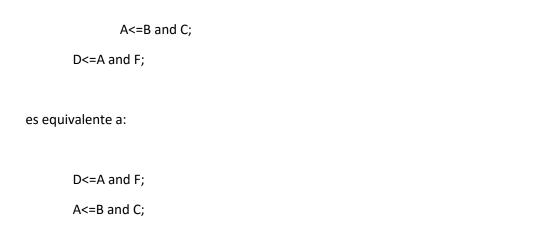

Un circuito electrónico es, por naturaleza paralelo, es decir, no existe un mecanismo inherente a la tecnología soporte que establezca precedencias en la actividad de sus bloques constituyentes. Esto significa que la descripción del mismo ha de preservar esta propiedad. Cuando se introducen sentencias o bloques (que más adelante llamaremos procesos), todos ellos son <u>concurrentes</u>, es decir, no existe orden de prelación entre unos u otros (en lo que afecta a su funcionalidad, que no es lo mismo que su legibilidad e interpretación). Por ejemplo:

sin embargo existen gran cantidad de situaciones en las que es muy fácil describir un comportamiento de un circuito de modo secuencial.

Nos obstante, formalmente existen en VHDL cinco tipos de elementos concurrentes:

- Bloques (block). Grupos de sentencias concurrentes.

- Instancias de componentes. En diseños estructurales, cada vez que se produce la utilización de un componente se realiza de modo concurrente.

- Sentencias **generate**. Generación de copias de bloques de hardware.

- Llamadas a procedimientos y funciones (**procedure** y **function**). Los procedimientos son algoritmos combinacionales que computan y asignan valores a señales. Suelen formar parte de librerías.

- Declaración y definición de procesos (process). Internamente definen algoritmos secuenciales que leen valores de señales y asignan valores a señales, aunque externamente el proceso se ve como una instancia concurrente.

- Asignaciones de señales computadas a través de expresiones booleanas o aritméticas.

Resulta, pues muy útil la presencia de mecanismos que permitan introducir código secuencial. El más común es el proceso o **process**, que detallaremos en el siguiente apartado. Un proceso es un bloque que contiene código secuencial pero externamente se contempla como un bloque concurrente, y tiene el mismo tratamiento que el ejemplo anterior. Las

instancias de componentes se han tratado en el capítulo anterior y los procedimientos y las funciones se explicarán en el capítulo seis cuando se explican las librerías, ya que es en ellas donde más se utilizan.

# 2. Estructura de un proceso

Para comprender el funcionamiento de un proceso conviene introducir una doble perspectiva del mismo: la simulación y la síntesis. Desde el punto de vista de simulación el proceso contiene una secuencia de transformaciones sobre las señales que se producen una vez activado el mismo. Desde el punto de vista de síntesis conviene no olvidar que un proceso representa una porción de un circuito y que es preciso asociar una imagen hardware al conjunto de sentencias que lo componen.

El mecanismo del **process** se entiende como una manera fácil de transferir algoritmos ensayados en lenguajes de alto nivel secuenciales a VHDL. Esta idea condiciona enormemente su sintaxis y sus posibilidades.

#### 2.1 Elementos de un proceso.

El siguiente listado recoge todos los elementos de un proceso

etiqueta\_proceso: **PROCESS**(lista de sensibilidad) **VARIABLE ...**BEGIN

--secuencia de ordenes

--secuencia de orden END PROCESS etiqueta\_proceso;

Los procesos se introducen en la zona de arquitectura y no existe restricción alguna acerca de su número y extensión.

#### 2.2 Lista de sensibilidad.

La lista de sensibilidad es un artificio para realizar computacionalmente el paralelismo, principalmente en simulación, aunque también es útil en síntesis. La lista de sensibilidad es un conjunto de señales que activan el proceso, es decir, mediante un cambio en un cualquiera de ellas, el proceso es evaluado completamente. Esto permite resolver el problema de la concurrencia mencionado, ya que si una sentencia concurrente es evaluada cuando los argumentos de la sentencia varían, igualmente ocurre con una lista de sensibilidad.

Existen varias cuestiones que conviene aclarar:

- La lista de sensibilidad debe contener <u>todas las señales</u> que afecten a la evaluación del proceso, es decir, señales que usualmente se ubican a la derecha en una sentencia de asignación o evalúan una sentencia condicional.

- La omisión de una señal en la lista de sensibilidad afecta necesariamente a la morfología del circuito que representa.

- Si no existe lista de sensibilidad el proceso se denomina **infinito** y se ejecuta constantemente. Para su control se precisa el uso de sentencias tipo *wait* que son típicas de construcciones no sintetizables y se estudiarán en el capítulo correspondiente.

- Si una señal que se computa a la **izquierda** de una asignación dentro del proceso aparece en la lista de sensibilidad, este se evaluará de nuevo, y se producirá sucesivamente hasta que el valor de la señal se estabilice.

- Si se omitiese una señal de entrada en la lista de sensibilidad, este se evalúa cuando una de las señales restantes de la lista cambie, por tanto dicha señal habría de almacenarse hasta el cambio. Se generaría, pues, un *latch* no deseado.

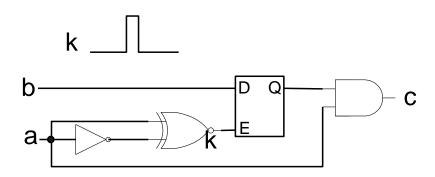

Por ejemplo, si en la lista de sensibilidad se omite una señal, hemos dicho que afecta decididamente a la imagen hardware que se representa. Imaginamos el siguiente ejemplo:

pr1: **PROCESS**(a)—omitimos la señal b **BEGIN**c<=a and b; **END PROCESS** pr1;

Se ha omitido la señal *b*. Cuando *a* varía el proceso se evaluará realizando la operación *and* de *a* y *b*, con el valor que *b* tenga en ese instante. Sin embargo, cuando *b* varía *c* no se actualizará, ya que no está en la lista de sensibilidad. De esta manera, el circuito que produce el valor de c ha de almacenar el valor de b cuando se produzca una variación en a. La figura representa un circuito equivalente a la situación expresada. El circuito activa el match es un detector de flanco, que se basa en la presencia de un retardo en la entrada de la puerta XNOR, que genera la forma de onda indicada en el punto k, con un pulso de anchura el retardo del inversor. Esta situación no es admisible desde el punto de vista de un diseño, ya que el retardo del inversor es dependiente de la tecnología, y es tan estrecho que es probable que viole las condiciones temporales de la entrada de habilitación E del *latch*.

Dado que este circuito no es aceptable casi todos los programas de síntesis producen un aviso de ausencia de una señal de la lista de sensibilidad, aviso que es preciso eliminar, y

dejan a que el diseñador, si quiere implementar estructuras como estas, describa explícitamente el circuito.

#### 2.3 Declaración del tipo variable

En la implementación secuencial se suele hacer uso de variables temporales que no trascienden fuera del proceso. Su uso está limitado a asignaciones en su interior. Este recurso del lenguaje se le conoce como **variable**. El mecanismo de asignación es igual que el de una señal, con la salvedad de que en la asignación se utilizan los símbolos ':=' en lugar del '<='. Por ejemplo:

```

asig: PROCESS(b,c)

VARIABLE a: std_logic;

BEGIN

a:= b and c;

d<= a xor b;

END PROCESS asig;

```

La variable 'a' aparece en una situación transitoria, y tiene una misión aclaratoria, es decir, un proceso se activa con señales y resuelve los valores de señales. Existen, además, otras diferencias cualitativas que describiremos en el apartado siguiente.

#### 2.4 Asignaciones dentro de un proceso

En el cuerpo de un proceso se admiten asignaciones simples. La principal diferencia en el tratamiento estriba en que el proceso se evalúa en un instante de tiempo cero, es decir, que todas las asignaciones y condiciones se producen sin retraso. De la misma manera las asignaciones a señales (que no a variables) dentro de un proceso no se hacen efectivas hasta que el proceso no se concluye. Por ejemplo:

```

ARCHITECTURE comport OF ejemplo SIGNAL q: INTEGER RANGE 0 TO 3; BEGIN ej: PROCESS(A,B,...)

BEGIN q<=0; IF(A='1') THEN q<=q+1; END IF; IF(B='1') THEN q<=q+2; END IF; CASE q=> WHEN 0=> ....

END CASE; END PROCESS ej; END comport;

```

El valor de q no se actualiza hasta que el proceso ha concluido. Esto significa que en la evaluación realizada en la estructura CASE el valor de q es el que tuviese antes de la evaluación del proceso. Ni siquiera la asignación incondicional afectaría a dicha evaluación. Para realizar

una evaluación secuencial tal y como se realiza en un programa desarrollado para una CPU es preciso utilizar variables en vez de señales, es decir:

```

ARCHITECTURE behav OF ejemplo BEGIN  \begin{array}{c} ej: \textbf{PROCESS}(A,B,..) \\ \textbf{VARIABLE } q: \textbf{INTEGER RANGE } 0 \textbf{ TO } 3; \\ \textbf{BEGIN} \\ q:=0; \\ \textbf{IF}(A='1') \textbf{ THEN } q:=q+1; \textbf{ END IF}; \\ \textbf{IF}(B='1') \textbf{ THEN } q:=q+2; \textbf{ END IF}; \\ \textbf{CASE } q => \\ \textbf{WHEN } 0 => \\ \dots \\ \textbf{END CASE}; \\ \textbf{END PROCESS } ej; \\ \textbf{END behav}; \end{array}

```

Mediante esta modificación realizamos la asignación deseada y la funcionalidad que resulta es la requerida.

# 2.5 Sentencias propias de un proceso

Dentro de un proceso existen un conjunto de sentencias que son propias de su estructura. Fuera de él carecen de significado. Son condiciones no concurrentes:

#### Sentencia IF THEN ELSIF ELSE

La condicional se resuelve mediante la sentencia IF. Su sintaxis es:

```

IF condición 1THEN

Consecuencia 1;

ELSIF condición 2 THEN

Consecuencia 2;

ELSIF ... THEN

...

ELSE

Consecuencia por defecto;

END IF;

```

La condición puede ser lógica o aritmética. Merece especial atención al concepto inherente de jerarquía que introduce la sentencia IF. La condición 1 es previa a la condición 2, que nunca será evaluada en caso de cumplimiento de la primera. Algo parecido ocurre con la siguiente estructura anidada, también válida:

```

IF condición 1THEN

IF condición 2 THEN

Consecuencia 2.1;

ELSE

Consecuencia 2.2;

END IF;

ELSE

Consecuencia por defecto;

END IF;

```

La diferencia entre ambas estructuras estriba en que en la segunda las consecuencias 2.1 y 2.2 se validan mediante un circuito que comprueba Condición 1 y Condición 2 encadenadas. En la primera de las estructuras la Consecuencia 1 tendría un camino crítico menor.

Las condiciones en una sentencia IF se evalúan a través de expresiones booleanas que devuelven los valores 'verdadero' o 'falso'. En la siguiente tabla se resumen los tipos de expresiones:

| Tipo de condición | Ejemplo                                                                           | С                                          |

|-------------------|-----------------------------------------------------------------------------------|--------------------------------------------|

| =                 | If (a = b) then                                                                   | Igualdad.                                  |

| /=                | If (a /= b) then                                                                  | Desigualdad                                |

| <,<=,>,>=         | If (a <b) th="" then<=""><th>Menor, menor o igual, mayor, mayor o igual</th></b)> | Menor, menor o igual, mayor, mayor o igual |

# <u>Inferencia de elementos de memoria</u>

Las sentencias condicionales tienen una particularidad que las hacen de especial interés en la síntesis de hardware secuencial. Sea el ejemplo siguiente:

```

sec: PROCESS(ena,d)

BEGIN

IF (ena='1') THEN

q<=d;

qz<=NOT d;

END IF;

END PROCESS sec;

```

La estructura inferida hace que q tome el valor d cuando ena tiene el valor '1'. Pero, ¿qué ocurre cuando *ena* vale '0'? Si cambia d, q permanece con el valor de d cuando *ena* valía '1'. Existe un dispositivo hardware que permite realizar la funcionalidad expuesta, consistente en un elemento de memoria activo por nivel o *latch*. Del ejemplo se infiere un *latch* para la señal q y otro para la qz, que en un posterior proceso de optimización sería agrupado en uno solo con la negación de q.

El modelo de inferencia de un *latch* se reproduce continuamente durante el proceso de diseño, en situaciones deseadas y en situaciones no deseadas. Un ejemplo típico de situación deseada es el *biestable*, donde la señal *ena* es el reloj, y por tanto se ha de utilizar un mecanismo para especificar el flanco del reloj, mecanismo que se expondrá en el capítulo cuarto. El *latch* rara vez se utiliza en diseño síncrono y suele ser una fuente de problemas. Normalmente cuando los programas de síntesis detectan una estructura de un *latch* (no deseada, el biestable es un elemento siempre deseado) suelen proporcionar un aviso de que se infiere. En general es una estructura condicional que no tiene solución hardware para todas las posibles situaciones. Por tanto es recomendable que en las estructuras que dependen de la evaluación de una condición antecedente dispongan al menos de una valor por defecto para los consecuentes.

Sentencia CASE WHEN

Una selección en función del valor que toma una señal se construye mediante la selección

CASE objeto IS

Código para el resto de los casos;

END CASE;

En los casos en que las dos formas son posibles, es recomendable el uso de CASE antes que IF/ELSIF dado que el IF introduce un elemento de prioridad que puede resultar menos eficiente (más área).

WHEN OTHERS representa la condición por defecto. No puede haber dos valores de selección iguales y la cláusula **others** debe aparecer si no se cubren todos los posibles valores de selección.

Es importante que exista una asignación para todas las salidas en cada uno de los casos ya que de esta forma evitamos la formación de *latches* indeseables.

Bucles dentro de procesos

VHDL permite la construcción de bucles para reducir el tamaño de código repetitivo. Estas sentencias han de ir en dentro de un proceso.

```

Etiqueta: FOR parámetro IN lista_de_valores LOOP

Código;

END LOOP Etiqueta;

Etiqueta: WHILE condición LOOP

Código;

END LOOP Etiqueta;

```

Cuando el objeto a evaluar es un índice, no es precisa su declaración previa. En ambos casos es posible interrumpir la evaluación normal con las instrucciones NEXT y EXIT, cuando la condición se satisface. NEXT salta el resto del código secuencial dentro del bucle y obliga a la evaluación de un nuevo índice. EXIT salta el resto del código secuencial y obliga a la terminación del mismo, continuando con la secuencia del proceso.

```

NEXT etiqueta WHEN condición; --saltar el resto del bucle EXIT etiqueta WHEN condición; --salir del bucle

```

por ejemplo:

```

FOR i IN 0 TO 7 LOOP

NEXT WHEN i=6; -- Dejamos el bit 6 como estaba

Bus(i) <= '0';

END LOOP;

Otra alternativa es:

i:=0;

WHILE i < 8 LOOP

Bus(i) <= '0';

i:=i+1;

END LOOP;

```

# 3. Bloques de sentencias

Es una agrupación de sentencias concurrentes. La sintaxis es:

```

etiqueta: BLOCK

BEGIN

Sentencia Concurrente 1;

Sentencia Concurrente 2;

Sentencia Concurrente 2;

......

END BLOCK etiqueta;

```

Normalmente un bloque no crea un nuevo nivel de jerarquía. Su función es puramente aclaratoria y en la práctica es poco utilizado.

# 4. Asignaciones concurrentes

Es posible realizar operaciones de asignación concurrente equivalentes a las que se han definido dentro de las estructuras secuenciales, en las que las restricciones a la hora de realizar una inferencia son exactamente las mismas que en las mencionadas estructuras, con la ventaja de que no es preciso la realización de una estructura del tipo proceso.

NOTA: Hemos comentado que realmente todos los elementos concurrentes son tratados dentro del complejo tratamiento informático del lenguaje como **process**, concurrentes entre sí.

### 4.1 Asignación simple

Es la sentencia concurrente más elemental y se realiza mediante el asignador '<='. La condición para una correcta asignación es la igualdad en los tipos de las señales que se asignan. Su sintaxis es:

etiqueta: Señal Destino <= Señal Origen;

Donde la señal destino puede ser una señal declarada previamente mediante **signal** o bien una señal que se encuentra en el puerto (**port**) de la entidad (**entity**) como salida, tipo **out** , entrada-salida **inout** (ó **buffer**, cuando se admita).

La señal origen puede ser una señal declarada previamente mediante **signal** o bien una señal que se encuentra en el puerto (**port**) de la entidad (**entity**) como entrada (**in**), entradasalida (**inout**) (ó **buffer**, cuando se admita). Además la asignación simple permite la evaluación de expresiones siguiendo una sintaxis igual:

etiqueta : Señal Destino <= Expresión Funcional;

La expresión funcional representa una función booleana o aritmética que es combinación de señales de entrada o señales. La siguiente tabla representa las funciones booleanas que se admiten en una asignación:

| Operador | Ejemplo     | Tipo            |  |

|----------|-------------|-----------------|--|

| NOT      | a <= NOT b; | Operador lógico |  |

| AND, NAND  | a <= b AND c; | Operadores lógicos |  |

|------------|---------------|--------------------|--|

| OR,NOR,XOR | a <= b OR c;  | Operadores lógicos |  |

Asimismo se admiten operaciones aritméticas. Estas operaciones han de estar previamente definidas en librerías. En el capítulo cuarto se tratan más en profundidad la manera de trabajar con estas funciones. Por ahora nos limitaremos a exponer una relación de las mismas:

| Operador | Uso           | Descripción                          |  |

|----------|---------------|--------------------------------------|--|

| *        | a <= b * c;   | Multiplicación                       |  |

| **       | a <= b ** 2;  | Exponencial                          |  |

| /        | a <= b/c;     | División (c ha de ser potencia de 2) |  |

| +        | a <=b+c;      | Suma                                 |  |

| -        | a <=b-c;      | Resta                                |  |

| MOD      | a <= b MOD c; | Calcula <b>b</b> en modulo <b>c</b>  |  |

| REM      | a <= b REM c; | Calcula la resta entera de b / c     |  |

Es posible una asociación y una inferencia de jerarquía en las funciones jerarquía mediante la utilización de paréntesis. Existe una prioridad en la definición de las funciones. Se resume en la siguiente tabla:

# 4.2 Asignación condicional

Es una expresión concurrente que realiza las mismas operaciones que la cláusula IF dentro de un proceso. Su sintaxis es:

etiqueta: Señal Destino <= Expresión1 **WHEN** Condición **ELSE** Expresión2;

No existen diferencias cualitativas entre ambos tipos de sentencias. La forma IF admite, de modo mucho más legible, más de una consecuencia y consecuencias mucho más complejas que la forma concurrente WHEN.

De la misma forma es posible encadenar la forma WHEN:

```

etiqueta: Señal Destino <= Expresión1 WHEN Condición1 ELSE

Expresión2 WHEN Condición2 ELSE

Expresión3 WHEN Condición3 ELSE

.............

ExpresiónN WHEN CondiciónN ELSE Expresión;

```

4.3 Selección en forma concurrente

También existe una sentencia equivalente a case en forma concurrente. Su sintaxis es:

```

etiqueta: WITH expresión_selección SELECT