## Tema 3: VHDL avanzado

Hipólito Guzmán Miranda

Departamento de Ingeniería Electrónica

Universidad de Sevilla

hguzman@us.es

## Contexto docente

- Arquitectura de FPGAs

- VHDL avanzado

- Capacidades de verificación funcional en Circuitos Digitales

## Conocimientos previos requeridos:

- VHDL básico (SEC GITT / Complementos de Electrónica MUIT)

- Diseño con dos procesos

## Objetivos de aprendizaje

- Ampliar el vocabulario de sentencias y palabras clave en VHDL

- Familiarizarse con el potencial de VHDL para elevar el nivel de abstracción en diseño, sin perder de vista el comportamiento en síntesis

- Adquirir capacidades para reducir la duplicidad de código e incrementar su reutilizabilidad

## Repaso

### FPGAs:

- IOBs, CLB, rutado, (re)programabilidad

SoC:

- Soft processors vs. hard macro

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

#### Motivación

## El VHDL que conocéis (síntesis)

```

comb: process (< lista de sensibilidad>)

if ... elsif ... else ... end if;

case ... when => ... end case;

sinc: process (<lista de sensibilidad>)

if (rst = '1') then ...

elsif (rising edge(clk) then ...

end if;

```

Instancias de componentes

#### Motivación

## El VHDL que conocéis (simulación)

clk\_process: process

invertir clk, wait for clk\_period/2

stim process: process

Secuencia de estímulos generada manualmente (muy tedioso en tests complejos)

## 'Cargo cult programming'

En C, código descuidado normalmente produce malos resultados, y es más difícil de depurar y modificar

En VHDL, código descuidado puede producir hardware que funcione, pero también será difícil de depurar y modificar -> código que nadie quiere tocar

#### Motivación

## VHDL es un lenguaje de ALTO nivel

- Describid a un mayor nivel de abstracción

- Dejad que el sintetizador infiera el circuito

- El hardware sintetizado funciona igual de bien (o mejor), pero el código es más sencillo de leer y mantener

Pero vayamos poco a poco...

## Unas palabras de advertencia

Todo lo que se explica aquí cuesta recursos hardware (en implementación)

Las operaciones no se realizan secuencialmente sino concurrentemente

Paradigma de diseño es el mismo: operaciones se convierten en lógica -> pero tendréis más recursos para estructurar vuestro código

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

## El tipo de dato record

"Bad programmers worry about the code. Good programmers worry about data structures and their relationships." - Linus Torvalds

- Esto también aplica cuando describimos hardware

- Los records son un tipo de dato que está compuesto de otros datos

- Son el equivalente VHDL a los 'structs' de C

- Agrupad señales o puertos del mismo contexto en records

## Ejemplo: signals

```

type transceiver_data is

record

data : std_logic_vector (15 downto 0);

valid : std_logic;

end record;

signal datain, dataout : transceiver_data;

```

## Ejemplo: puertos

```

entity transceiver is

Port (

: in std logic;

clk

: in std logic;

rst

data in : in transceiver data;

data out I : out transceiver data;

data out Q : out transceiver data

end transceiver;

```

## Ejemplo: puertos

entity transceiver is

- El record entero tiene que tener una única dirección (IN o OUT)

- Añadir una nueva señal al puerto sólo implica cambiar la definición del record!

```

data_out_Q : out transceiver_data

);

end transceiver;

```

## Asignación y uso

Acceder a record.dato:

```

if (data_in.valid = '1') then

data_out.data <= data_in.data;

data_out.valid <= '1';

end if;</pre>

```

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

# U SEVILL

#### **Functions**

## Leer señales, devolver valor

```

function invert (data: std_logic) return std_logic is

begin

return not data;

end function invert;

```

Cada llamada a la función generará un inversor al sintetizar!

# THERSIDAD OF SEVILL

#### **Functions**

## **Ejemplos**

```

function sum (a: integer; b: integer)

return integer is

begin

return a+b;

end function sum;

```

Cada llamada a la función generará un sumador al sintetizar

# THERSIDAD OF SEVILL

#### **Functions**

## **Ejemplos**

```

function sel (cond: boolean; if true,

if false: integer) return integer is

begin

if cond = true then

return (if true);

else

return (if false);

end if;

end function sel;

```

#### **Functions**

## ¿Por qué usarlas?

Ya que producen el mismo hardware, merece la pena usarlas para:

- Encapsular operaciones que reutilizas

- Multiplexar o invertir generics, constants o señales en un generic map o port map

Insisto: no son subrutinas, son hardware!

#### **Procedures**

## Múltiples entradas, múltiples salidas

Aparentemente similares a los functions pero:

Tienen parámetros IN y OUT

Pueden leer de los IN y modificar los OUT

#### **Procedures**

## **Ejemplo:**

```

procedure vect_write

(constant data: in std_logic_vector(31 downto 0);

signal vector_ctrl : out fifo_ctrl) is

begin

vector_ctrl.datai <= data;</pre>

vector_ctrl.wr_en <= '1';</pre>

wait for 10 ns;

vector_ctrl.wr_en <= '0'; --after 10 ns;</pre>

end procedure;

```

(No es sintetizable ya que contiene un wait)

## Functions y Procedures

### **Diferencias:**

Las funciones no modifican nada, simplemente devuelven un valor

```

data <= a_function (other_data);</pre>

```

Los procedimientos cambian el valor de señales

```

my procedure (signals in, signals out);

```

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

#### **Bucle for**

## for i in 0 to 7 loop

- El sintetizador expande el bucle durante la síntesis

- El rango del bucle debe ser estático (para que pueda sintetizarse)

- Cada paso por el bucle no es una 'iteración', sino una repetición del hardware

## **Ejemplo**

```

reorder_data: process (data_in)

begin

for i in 0 to 7 loop

data_out(i) <= data_in(7-i);

end loop;

end process;</pre>

```

## For loop

## Es equivalente a:

```

reorder_data: process (data_in)

begin

data_out(0) <= data_in(7);</pre>

data_out(1) <= data_in(6);</pre>

data_out(2) <= data_in(5);</pre>

data_out(3) <= data_in(4);</pre>

data_out(4) <= data_in(3);</pre>

data_out(5) <= data_in(2);</pre>

data_out(6) <= data_in(1);</pre>

data_out(7) <= data_in(0);</pre>

end loop;

end process;

```

## Instanciación condicional de componentes

- Instancia un componente o no, según se cumpla o no una condición

- Esta condición debe ser estática de forma que se sepa si se cumple durante la síntesis

El sintetizador es el que instancia o no el componente

## if condition generate

```

second_instance: if GENERATE_TWO=true

generate

inst2: cont port map (

clk => clk,

rst => rst,

count => count2 );

end generate second_instance;

```

## Instanciación múltiple de componentes

- Usando for parameter in range

- Al igual que antes, el sintetizador expande el bucle durante la síntesis

- El rango del bucle debe ser estático (para que pueda sintetizarse)

- Cada paso por el bucle no es una 'iteración', sino una instancia del componente

## for parameter in range generate

```

regdesp:

for i in 0 to 3 generate

myreg : reg port map (

clk \Rightarrow clk

rst => rst,

din => data(i),

dout => data(i+1));

end generate regdesp;

```

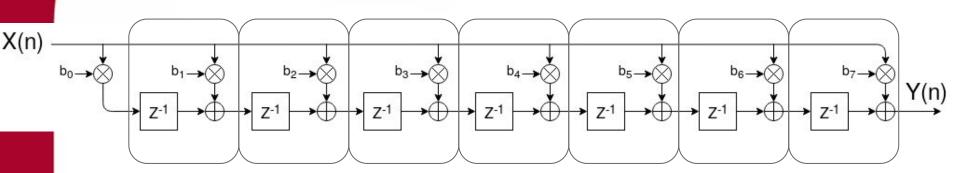

## Filtro FIR

## Como conjunto de etapas

```

channel_filter: for i in 0 to 23 generate

taps: tap generic map(

INPUT_WIDTH => 9,

OUTPUT WIDTH => 10,

TRUNC_BITS => 8,

=> coefs(sel(i<12, i, 23-i)),</pre>

COEF

SAT_MULT_BITS => 2)

port map(

clk \Rightarrow clk,

rst => rst,

valid => cfilterin_valid,

input => cfilterin,

prev => d aux(i),

output => d_aux(i+1)

end generate;

```

#### VHDL avanzado

## Contenido

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

# Packages

# Encapsular todo lo anterior

En un package VHDL podemos definir:

- Tipos de datos

- Constantes

- Funciones

- Procedimientos

- Componentes

# **Packages**

# Encapsular todo lo anterior

En lugar de redeclarar todo lo que necesitemos en cada vhd de cada entidad, simplemente añadimos a la sección library:

use work.mypackage.all;

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

```

#### package mypackage is

- -- declaración de tipos de datos

- -- declaración de constantes

- -- declaración de componentes

- -- declaración de funciones y procedimientos

#### end mypackage;

#### package body mypackage is

-- definición de funciones y procedimientos

#### Libraries

# Conjuntos de packages

Se incluyen por completitud, pero no os hará falta crearlas para la asignatura

Por ejemplo, std\_logic\_1164 es un package del library IEEE:

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

```

Vuestros packages custom pertenecen al library work por defecto

# Libraries

# Conjuntos de packages

Para utilizar libraries de terceros, deben compilarse/sintetizarse aparte, y en la sección library:

```

library uvvm_util;

use uvvm_util.types_pkg.all;

use uvvm_util.string_methods_pkg.all;

use uvvm_util.adaptations_pkg.all;

use uvvm_util.methods_pkg.all;

use library>.<package>.all;

```

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

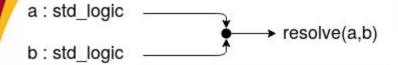

# std\_ulogic: no resuelto std\_logic: resuelto

```

TYPE std ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

```

## Función de resolución

```

-- resolution function

CONSTANT resolution table : stdlogic table := (

| U X 0 1 Z W L H - | |

('U', 'X', '0', 'X', '0', '0', '0', 'X'), -- | 0 |

('U', 'X', 'X', '1', '1', '1', '1', 'X'), -- | 1 |

('U', 'X', 'O', '1', 'Z', 'W', 'L', 'H', 'X'), -- | Z |

('U', 'X', 'O', '1', 'W', 'W', 'W', 'X'), -- | W |

('U', 'X', 'O', '1', 'L', 'W', 'L', 'W', 'X'), -- | L |

('U', 'X', 'O', '1', 'H', 'W', 'W', 'H', 'X'), -- | H |

);

```

# ¿Qué significa esto?

a : std\_ulogic → ERROR!

- No siempre queremos esto! (de hecho, casi nunca lo queremos)

- El sintetizador te avisa de los multi-source

- Los simuladores no! (aparecen 'X' en los waveform)

Nos sirve de chequeo en tiempo de síntesis / compilación

# ¿Cuándo lo queremos?

#### Síntesis:

Puertos bidireccionales

#### Simulación:

- Modelado de pull-ups, pull-down, resistencias (fuera de nuestro diseño digital)

- Buses compartidos

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

# THERSIDA O OR SEVILL

#### Versiones del estándar

#### VHDL'87

- Primera versión

- VHDL'93

- Versión con mayor soporte por las herramientas de síntesis y simulación propietarias. Introduce variables compartidas

- VHDL 2002

- Añade tipos protegidos para variables compartidas. Se añade VHPI (VHDL Procedural Interface) en 2007

- VHDL 2008 (más información <u>aquí</u>)

- Integración de PSL (Property Specification Language).

Generics en tipos, paquetes y subprogramas. Soportado en síntesis por Synopsys, y en simulación por QuestaSim y

GHDL. Múltiples mejoras de usabilidad (process (all);)

- VHDL 2019

- Pendiente de aprobación

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

#### Para finalizar

# Conclusiones y recomendaciones

- VHDL da opciones para estructurar el código de manera que sea más mantenible

- No es obligatorio usarlo todo

- Aunque esté encapsulado, sigue siendo HW!

- Se recuerda que Xilinx ISE genera plantillas para todo lo mencionado anteriormente (en Project -> New source y en Edit -> Language Templates)

- Motivación

- Records

- Functions y Procedures

- Sentencias For y Generate

- Packages y Libraries

- std\_ulogic vs std\_logic

- Versiones del estándar

- Conclusiones

- Bibliografía

# **Bibliografía**

- Brian Mealy, Fabrizio Tappero, <u>Free</u>

<u>Range VHDL</u>. Free Range Factory, 2018

- The VHDL Golden Reference Guide.

Doulos, 1995

- Ricardo Jasinski, Effective Coding with VHDL: principles and best practice. The MIT Press, 2016

# Resultados de aprendizaje

- Saber utilizar el tipo record para reestructurar los datos procesados por un diseño

- Diferencias entre function y procedure

- Uso de for y generate para generar instancias de hardware

- Saber que se puede mover código común a un package para evitar duplicidad de código

- ¿Cuándo se debe utilizar std\_ulogic y cuándo std\_logic?