# Tema 5: Verilog para diseñadores de VHDL

Hipólito Guzmán Miranda

Departamento de Ingeniería Electrónica

Universidad de Sevilla

hguzman@us.es

#### Contexto docente

BT02: Lenguajes de descripción hardware

- Tema 3: VHDL avanzado

- Tema 4: VHDL para procesado de señal

- Tema 5: Verilog para diseñadores de VHDL

#### Conocimientos previos requeridos:

- VHDL básico (SEC GITT / Complementos de Electrónica MUIT)

- Diseño con dos procesos

# Objetivos de aprendizaje

- Tener un primer contacto con el lenguaje Verilog

- Conocer las diferencias entre Verilog y VHDL

- Ser capaz de describir módulos sencillos en Verilog

- Ser capaz de comprender módulos descritos en Verilog por terceros

## Repaso

VHDL para procesado de señal:

- Tipos de datos

- Punto fijo vs punto flotante

- Diseño de interfaces

- FIFOs y memorias

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

#### Motivación

# ¿Por qué aprender Verilog?

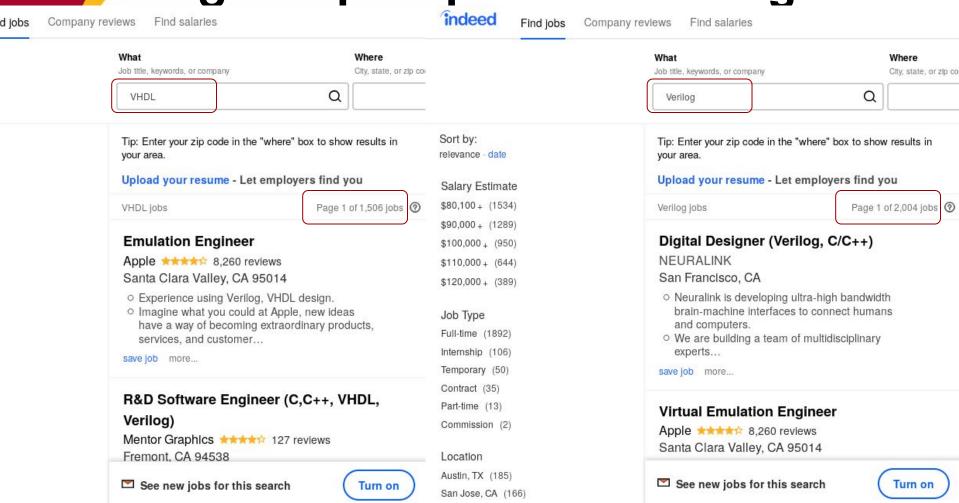

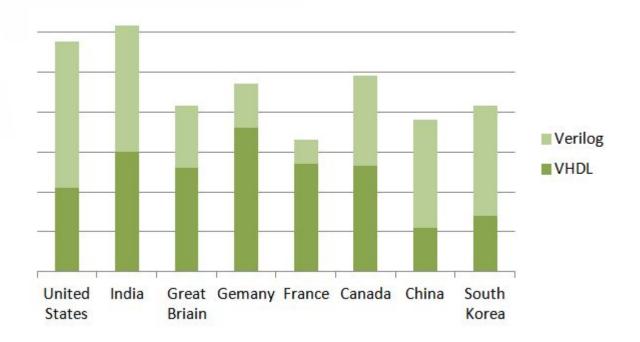

- Muchas empresas utilizan Verilog en lugar de VHDL

- Mejorar la empleabilidad (~2x)

- VHDL domina en Europa, Verilog domina fuera

- VHDL es preferido para aplicaciones críticas (aviónica, espacio, etc)

- Mucha verificación se hace utilizando Verilog o SystemVerilog (por ejemplo UVM)

- También hay alternativas usando VHDL (UVVM)

- Puede ser interesante hacer el diseño en un lenguaje y el testbench en otro

#### Motivación

# ¿Por qué aprender Verilog?

# ¿Por qué aprender Verilog?

Búsquedas de google Verilog vs VHDL (julio 2013 a julio 2014).

Fuente: <u>nandland</u>

#### Motivación

# ¿Por qué aprender Verilog?

- Entender código generado por terceros

- Otros diseñadores

- Código auto-generado por herramientas

- Soportado por Yosys Open Synthesis Suite

- VHDL soportado por el front-end propietario Verific (Yosys-vhdl disponible bajo licencia académica de Symbiotic EDA)

- En el futuro, ghdlsynth-beta podría sustituir a este front-end

- Es factible aprenderlo si sabemos VHDL y nos enfocamos en las diferencias entre ambos

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Verilog es un HDL

Al igual que con VHDL, no debemos perder de vista que las sentencias describen un hardware!

```

input a,

input b,

output o

);

assign o = ~(a & b);

endmodule

```

#### Introducción

## VHDL vs Verilog

- Tipado fuerte

- entity

- process

- sentencias concurrentes

- std\_logic con 9 valores

- Un tipo de asignación

- No existen operadores de reducción

- Tipado débil

- module

- always

- assign

- Tipos multievaluados tienen cuatro valores (0,1,Z,X)

- Dos tipos de asignaciones (blocking y nonblocking)

- Operadores de reducción

- wire y reg

- Bloques initial

- begin y end opcionales

- (si sólo hay una sentencia)

#### Introducción

## VHDL vs Verilog

- Sintaxis parecida a Ada

- Case-insensitive

- Comentarios de línea (--)

Más errores encontrados en tiempo de síntesis / compilación

- Sintaxis parecida a C

- Case-sensitive

- Comentarios de línea (//) y bloque (/\* ... \*/)

- Directivas de preprocesador (ifdef, ifndef, ...)

- Funciones de sistema (\$dumpfile, \$dumpvars, \$finish, \$display...)

- Código más compacto

En ambos se puede diseñar con uno o dos process/always, pero en Verilog está muy extendido el diseño con un único bloque always

```

library IEEE;

use ieee.std_logic_1164.all;

use ieee.numeric std.all;

entity counter is

port (clk, rst: in std logic;

Q: out unsigned (7 downto 0)

);

end counter;

architecture behavioral of counter is

signal count: unsigned(7 downto 0);

begin

process(clk, rst)

begin

if (rst='1') then

count <= (others=>'0');

elsif (rising edge(clk)) then

count <= count + 1;</pre>

end if;

end process;

Q <= count;</pre>

end behavioral;

```

#### VHDL vs Verilog:

## contador (1 proceso)

```

module counter

Verilog

input clk, rst,

output [7:0] Q

) ;

reg [7:0] count;

always @(posedge clk or posedge rst)

begin

count <= count + 8'b1;</pre>

if (rst) begin

count <= 8'b0;

end

end

assign Q = count;

endmodule

```

#### VHDL vs Verilog:

endmodule

```

VHDL

[...]

signal count: unsigned(7 downto 0);

signal p count: unsigned(7 downto 0);

begin

sinc: process(clk, rst)

begin

if (rst='1') then

count <= (others=>'0');

elsif (rising edge(clk)) then

count <= p count;</pre>

end if:

end process;

comb: process (count)

begin

p count <= count + 1;

end process;

0 <= count;</pre>

end behavioral:

```

#### contador (2 procesos)

```

Verilog

[\ldots]

reg [7:0] count;

reg [7:0] p count;

always @(posedge clk or posedge rst)

begin

count <= p count;</pre>

if (rst) begin

count <= 8'b0;

end

end

always @(count)

begin

p count <= count + 8'b1;</pre>

end

assign Q = count;

```

#### Introducción

# Estructura de un fichero Verilog

```

module <nombremodulo>

input <puerto1>, <puerto2>,

input [N-1:0] <puerto3>,

output [7:0] <puerto4>

) ;

reg [M-1:0] <reg1>;

reg <reg2>, <reg3>;

wire <wire1>;

always @(...)

begin

<sentencias...>

end

assign <destino> = <expresión>;

endmodule

```

- reg y wire pueden ser declarados en cualquier punto de la "arquitectura"

- Es buena práctica declararlos antes de usarlos!

- Todas las sentencias always y assign funcionan en paralelo

- Al igual que process y sentencias concurrentes

- También puede haber instanciación de módulos

- La veremos más adelante

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

# THERSIDAD OF SEVIK

#### Versiones del estándar

- Inicios (1980s)

- Lenguaje propietario de Gateway/Cadence

- Verilog-95

- Primera versión estandarizada

- Verilog 2001

- Mejoras de usabilidad, sentencia generate

- Versión con mayor soporte de los vendors

- Verilog 2005

- Correciones menores

- SystemVerilog

- Superset de Verilog 2005 que incluye múltiples funcionalidades para verificación y permite programación orientada a objetos

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Tipado débil vs tipado fuerte

# ¿Qué implica?

a es vector de 8 bits b es vector de 12 bits

VHDL (tipado fuerte) Verilog (tipado débil)

$a \leftarrow B; \rightarrow ERROR$

a  $\leq$  b;  $\rightarrow$  permitido

Perdemos datos: ¡buena suerte encontrando el error!

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Unidad básica de funcionalidad

VHDL: entity

Verilog: module

Ambos tienen puertos de entrada y salida, que se definen en una sección diferente a donde se define el funcionamiento

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Conjuntos de valores

Los datos predefinidos en verilog tienen dos (0, 1) o cuatro (0, 1, X, Z) valores posibles:

- 0 : cero lógico fuerte

- 1 : uno lógico fuerte

- X : valor lógico desconocido

- Z : alta impedancia

Al igual que en VHDL, X y Z no se suelen asignar en síntesis (salvo el caso particular de describir puertos triestado)

# Conjuntos de valores

#### 4-state (0, 1, X, Z):

- reg: vector definido por el usuario

- wire: vector definido por el usuario

- integer: 32-bit, signed

- time: 64-bit, unsigned

- logic: vector definido por el usuario (SV)

#### 2-state (0, 1) (SystemVerilog):

- shortint: 16-bit, signed

- int: 32-bit, signed

- longint: 64-bit, signed

- byte: 8-bit, signed

- bit: vector definido por el usuario

Modificadores: signed unsigned

#### Valores literales

[tamaño]'[signed][radix]valor

- tamaño en bits

- signed: s o S indica que el dato es con signo

- radix es la base:

- o b o B para binario

- u para octal

- h o H para hexadecimal

- o d o D para decimal

Los campos entre corchetes son opcionales

#### Valores literales

[tamaño]'[signed][radix]valor

#### Ejemplos:

```

2'b00, 32'hDEADBEEF, 4'b01XZ, 32'd10, 32'd0, 8'b0

```

## reg vs wire

#### reg

- Representa un objeto que almacena un valor entre una asignación y la siguiente

- Puede leerse en un bloque secuencial (always, initial) y en un bloque assign

- Puede asignarse en un bloque secuencial

- No puede asignarse en un bloque assign (sentencia concurrente)

- No tiene por qué implicar la síntesis de un registro

#### wire

- Representa un cable que conecta puertas o módulos

- Puede leerse en un bloque secuencial (always, initial) y en un bloque assign

- No puede asignarse en un bloque secuencial

- Puede asignarse en un bloque assign (sentencia concurrente) o como salida de un módulo instanciado

## reg vs wire

Ambos tipos pueden tomar 4 valores por bit (0, 1, X, Z)

La distinción realmente es en cómo se asignan (reg se asignan en always e initial, wire se asignan en assign y por submódulos instanciados)

¿Y... cómo asignamos los puertos?

- Puertos tipo input e inout se tratan como wire

- Puertos tipo output por defecto se tratan como wire, pero se pueden configurar como reg

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Asignaciones

# Verilog tiene 2 tipos de asignaciones

#### Blocking =

Bloquean la ejecución de las siguientes sentencias en un bloque secuencial (ej: always, initial) hasta que no termina la asignación

#### Non-blocking <=

No bloquean la ejecución (se realizan en paralelo)

No pueden utilizarse en los assign

En síntesis, normalmente las utilizaremos en los assign

En síntesis, normalmente las utilizaremos en los bloques secuenciales (initial, always)

#### Asignaciones

# Ejemplo blocking vs non-blocking

```

Signals

Waves

req rst = 0;

reg rst = 0;

10 ns

20 ns

Time

rst =0

initial begin

initial begin

rst <= #10 1'b1;

rst = #10 1'b1;

rst = #10 1'b0;

rst <= #10 1'b0;

rst = #10 1'b1;

rst <= #10 1'b1;

rst = #10 1'b0;

rst <= #10 1'b0;

rst = #10 1'b1;

rst <= #10 1'b1;

rst = #10 1'b0;

rst <= #10 1'b0;

# 20 $finish;

# 20 $finish;

end

end

```

Signals

Time

rst =0

Waves

10 ns 20 ns 30 ns 40 ns 50 ns 60 ns 70 ns 80 ns

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

## Operaciones aritméticas y lógicas

## **Operaciones**

- Not: ~

- And binaria: &

- Nand binaria: ~ &

- And "lógica": & &

- Or binaria: |

- Nor binaria: ~ ∣

- Or "lógica": ││

- Xor: ^

- Xnor: ~^

- Operaciones aritméticas:

```

+, -, *, /

```

#### Entre vectores:

- vect\_c <= vect\_a & vect\_b;</pre>

- vect\_c <= vect\_a | vect\_b;</pre>

#### Reducción:

(and de todos los bits de un vector, or de todos los bits, etc)

- bit\_b <= &vect\_a;</pre>

- bit\_b <= |vect\_a;</pre>

## Operaciones aritméticas y lógicas

# Operadores de comparación

- Igual: ==

- Distinto: !=

- Mayor que: >

- Mayor or igual que: >=

- Menor que: >

- Menor o igual que: <=</li>

- "Case equality": ===

- "Case inequality": !==

- Permiten comparar con X y

Z, en simulación

- o Por ejemplo, a === 1'bz

- No deben usarse en síntesis

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

# Bloques always

# Equivalentes a process

```

always @ (evento)

begin

<sentencias>

```

end

- El evento es equivalente a la lista de sensibilidad

- En procesos síncronos:

- posedge clk (si no tiene reset o tiene reset síncrono)

- o posedge clk or posedge rst

(si tiene reset asíncrono)

- En procesos combinacionales:

- O a or b or c (lista de sensibilidad)

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

# Bloques initial

# Bloques secuenciales que se ejecutan una única vez

Equivalente a un always que sólo se ejecuta una vez, en tiempo 0

#### Dos usos:

- En simulación, para generar estímulos

- Para asignar los INIT values de registros en FPGA

- El valor de INIT de un biestable (el que toma cuando se programa el bistream) no tiene por qué coincidir con el de reset

# **Bloques** initial

### Dos usos:

● En simulación, para ● Para asignar los generar estímulos

```

/* Pulse reset and stop

simulation */

req rst = 0;

initial begin

# 5 rst = 1;

# 20 rst = 0;

# 2600 $finish;

```

INIT values de registros en FPGA

```

initial begin

count <= 8'b0;

count2 <= 8'b0;

end

```

# Bloques initial

# Bloques secuenciales que se ejecutan una única vez

Si tenemos varios bloques initial en un módulo, ¿cuál se ejecuta antes?

Pueden darse condiciones de carrera entre ellos

Ej: un bloque initial que asigna un valor a A, en paralelo a otro bloque initial que asigna B <= A;

# Bloques always e initial

# ¿Qué sentencias podemos utilizar para control de flujo?

if case

endcase

```

if (condicion) begin

<sentencias>

end

else begin

<sentencias>

end

```

Verilog no tiene elsif, pero se puede usar if dentro de un else. begin y end son opcionales si sólo hay una sentencia

# Bloques always e initial

# ¿Qué sentencias podemos utilizar para control de flujo?

if case

```

if (enable) begin

p_count <= count + 1;

end

else begin

p_count <= count;

end</pre>

```

Verilog no tiene elsif, pero se puede usar if dentro de un else. begin y end son opcionales si sólo hay una sentencia

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

#### Assertions

# Equivalentes a las de VHDL

assert (condition);

```

assert (actual == expected);

assert (self_destruct == 1'b0);

assert (state != ERROR_STATE);

```

Utilizaremos los Assertions de Verilog para verificación formal.

SVA (SystemVerilog Assertions) tiene expresiones más potentes aún (implicación, propiedades, secuencias...), pero pocas herramientas las soportan (ej: QuestaSim).

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

#### Instanciación de módulos

# No es necesario declararlos como componente

```

nombremodulo nombreinstancia (

.puertomodulo ( wire del top ),

.puertomodulo2 ( wire del top2 ),

[...]

.puertomoduloN ( wire del topN )

counter uut (

.clk (clk),

.rst ( rst ),

.Q (value)

```

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

# **Conclusiones**

- Verilog es un lenguaje de descripción hardware y permite hacer lo mismo que permite VHDL

- El tipado débil de Verilog hace que sea más fácil equivocarse pero evita tener que usar funciones de conversión

- Cada diseñador tendrá sus preferencias

- Es importante prestar atención a las diferencias entre ambos lenguajes!

- Cuidado con reg/wire, blocking/nonbloking, initial...

- El lenguaje tiene más funcionalidades de las que hemos visto aquí

- Packed vs unpacked arrays, ifdef, \$dumpvars, \$readmem,

. . .

### Recomendaciones

Que la primera línea de todos vuestros ficheros Verilog sea:

#### `default nettype none

Para asegurar que las herramientas os dan un error si intentáis usar un reg/wire que no esté declarado (si no, suele ser complicado de depurar)

Si diseñáis con Verilog, existen 'linters' de Verilog que analizan vuestro código buscando errores comunes

- Motivación

- Introducción

- Versiones del estándar

- Tipado débil vs tipado fuerte

- Módulos

- Tipos de datos

- Asignaciones

- Operaciones aritméticas y lógicas

- Bloques always

- Bloques initial

- Assertions

- Instanciación de módulos

- Conclusiones

- Bibliografía

# **Bibliografía**

- Peter Wilson, Design Recipes for FPGAs using Verilog and VHDL. Elsevier, 2016

- Stuart Sutherland, Don Mills, Verilog and SystemVerilog Gotchas: 101 Common Coding Errors and How to Avoid Them. Springer, 2007

- Nazeih Botros, HDL with Digital Design: VHDL and Verilog. Mercury Learning and Information, 2015

# Resultados de aprendizaje

- ¿Podrías enumerar las diferencias principales entre VHDL y Verilog?

- Dada una lista de palabras clave de Verilog, indicar a qué palabras clave de VHDL equivalen

- Qué son reg y wire y cuándo se pueden asignar

- Diferencias entre =, <=, ==, ===</li>

- ¿Cuándo podemos prescindir de begin y end en sentencias Verilog?