## Tema 5

#### Circuitos Combinacionales

De cómo construir pequeñas células combinacionales con eficicencia

- Introducción

- 2. Puertas NAND y NOR

- Punto de conmutación

- 2. Layout de una puerta NAND y NOR

- 3. Generación de una función combinacional

- 4. Puertas XOR

- 5. Puertas lógicas con puertas de transmisión

- Diseñar circuitos integrados requiere un conocimiento detallado de la tecnología del fabricante elegido

- Diseñar significa conocer qué valores de los parámetros geométricos damos para obtener un comportamiento deseado.

- Las puertas CMOS heredan ciertas propiedades ya estudiadas en el inversor CMOS:

- Consumo estático cero

- Transistores p conectan a  $V_{\text{DD}}$  y transistores n conectan a  $V_{\text{GND}}$

- Cada entrada tiene un par de transistores, uno p y otro p

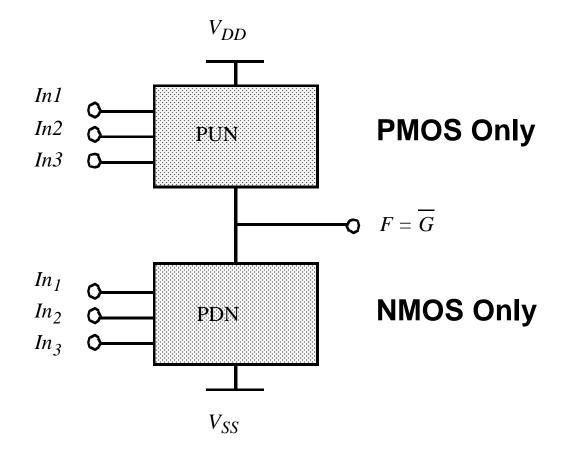

El esquema general de una puerta CMOS se puede describir de la siguiente manera:

#### **PUN and PDN are Dual Networks**

# Puertas NAND y NOR

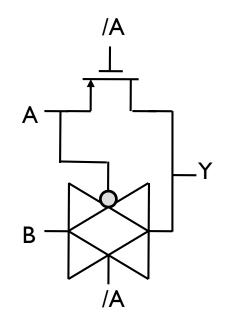

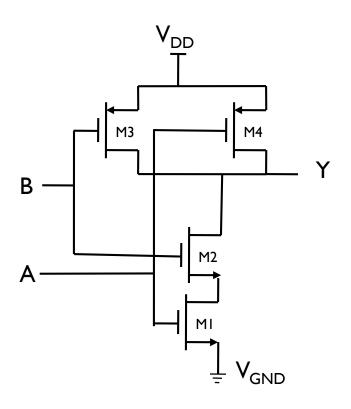

La puerta NAND de dos entradas tiene el esquema siguiente:

| A | В |     |     | M3  |     | Y |

|---|---|-----|-----|-----|-----|---|

| 0 | 0 | OFF | OFF | ON  | ON  | I |

| 0 | I | OFF | ON  | ON  | OFF | I |

| I | 0 | ON  | OFF | OFF | ON  | I |

| I | I | ON  | ON  | OFF | OFF | 0 |

Si M1=M2 y M3=M4:

$$W/L$$

<sub>M1</sub> =  $W/L$ <sub>M2</sub>  $W/L$ <sub>M3</sub> =  $W/L$ <sub>M4</sub>

Las dimensiones equivalentes:

Para MI y M2 están en serie

$$W/L_1+L_2$$

<sub>M12</sub>

Para M3 y M4 en paralelo

$$W_3 + W_4 / L$$

Ya que estamos considerando un inversor equivalente, podemos calcular los márgenes de ruido a partir de la ecuación del inversor

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2}}$$

$$1 + \sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2}$$

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}} V_{Tn} + (V_{DD} - V_{Tp})}{V_{SP} = V_{in}} = \frac{\sqrt{\frac{\mu_{n} \frac{W}{L_{1} + L_{2}}}{\mu_{p} \frac{W_{3} + W_{4}}{L}}} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}}}$$

$$1 + \sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}}$$

$$1 + \sqrt{\frac{\mu_{n} \frac{W}{L_{1} + L_{2}}}{\mu_{p} \frac{W_{3} + W_{4}}{L}}} V_{Tn} + (V_{DD} - V_{Tp})$$

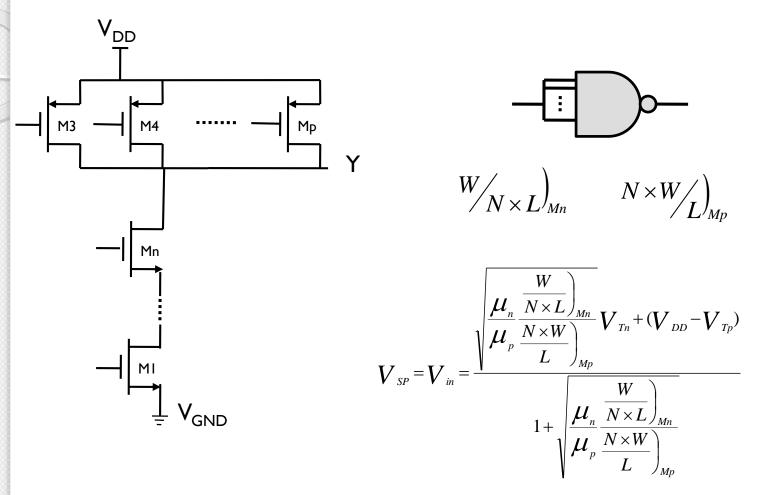

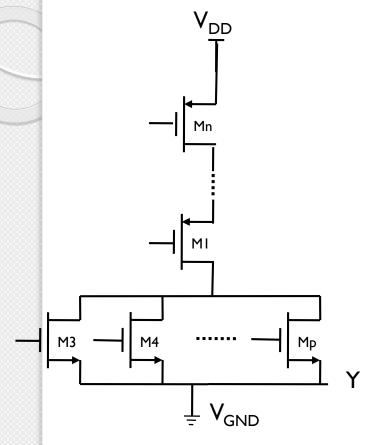

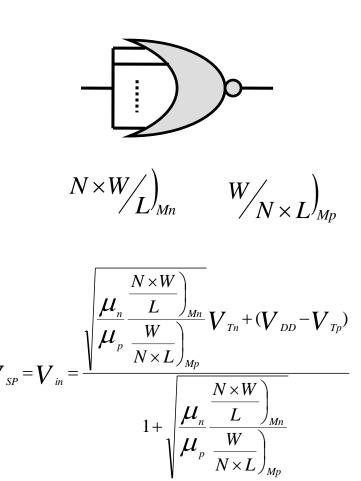

#### Extensión a N entradas

### Queda:

•

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_{n}}{\mu_{p}} \frac{W}{L}}_{Mn} V_{Tn}} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_{n}}{\mu_{p}} \frac{W}{L}}_{Mp}} \times \frac{1}{N}}$$

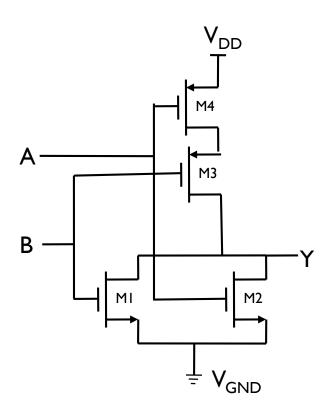

## La función NOR de dos entradas tiene el esquema siguiente

| A | В | MI  |     |     |     | Y |

|---|---|-----|-----|-----|-----|---|

| 0 | 0 | OFF | OFF | ON  | ON  | I |

| 0 | I | OFF | ON  | ON  | OFF | 0 |

| Ì | 0 | ON  | OFF | OFF | ON  | 0 |

| I | I | ON  | ON  | OFF | OFF | 0 |

### Si M1=M2 y M3=M4:

$$W/L \Big|_{M1} = W/L \Big|_{M2} \qquad W/L \Big|_{M3} = W/L \Big|_{M4}$$

#### Las dimensiones equivalentes:

Para MI y M2 están en paralelo

$$W_1 + W_2 / L$$

$M_{12}$

Para M3 y M4 están en serie

$$W/L_3+L_4$$

Ya que estamos considerando un inversor equivalente, podemos calcular los márgenes de ruido a partir de la ecuación del inversor

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2}}$$

$$1 + \sqrt{\frac{\mu_n}{\mu_p} \frac{W}{L}_n^2}$$

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}} V_{Tn} + (V_{DD} - V_{Tp})}{V_{SP}} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}}} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_{n} \frac{W}{L}}{\mu_{p} \frac{W}{L}}}} V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_{n} \frac{W_{1} + W_{2}}{L}}{\mu_{p} \frac{W_{1} + W_{2}}{L}}} V_{Tn}}}$$

#### Extensión a N entradas

### Queda:

$$V_{SP} = V_{in} = \frac{\sqrt{\frac{\mu_n \frac{W}{L}}{\mu_p \frac{W}{L}}} N \times V_{Tn} + (V_{DD} - V_{Tp})}{1 + \sqrt{\frac{\mu_n \frac{W}{L}}{\mu_p \frac{W}{L}}}_{Mp}} \times N$$

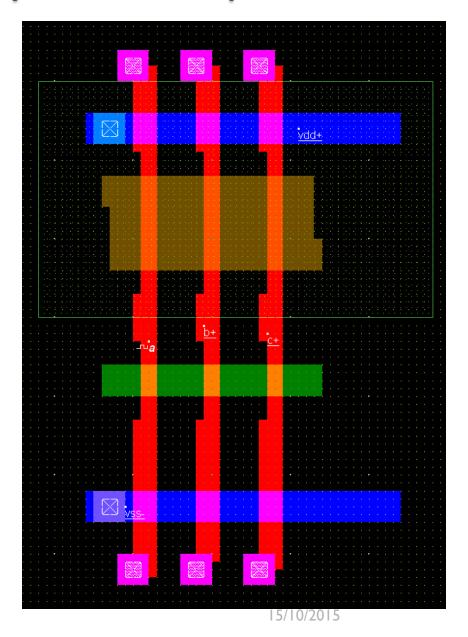

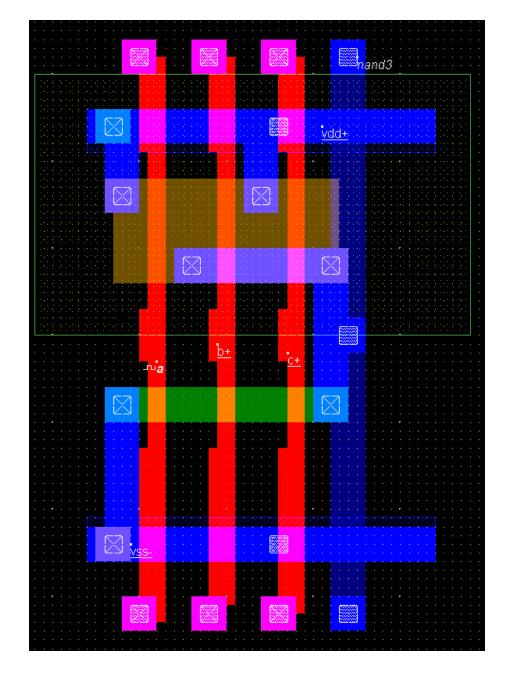

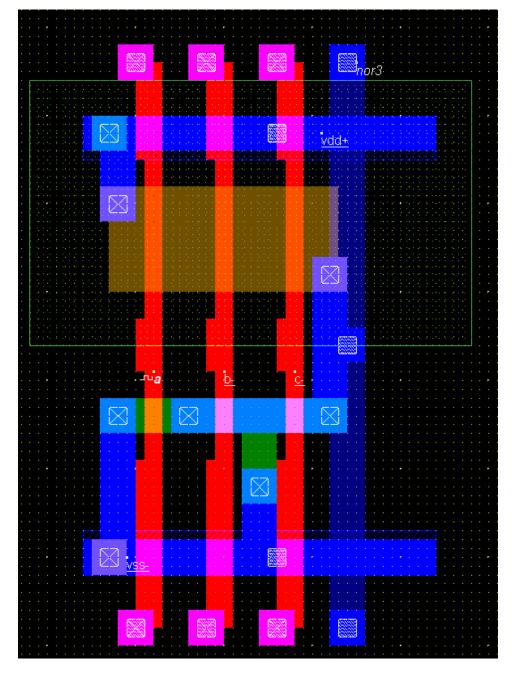

## 2.2 Layout de una puerta NAND y NOR

15/10/2015

Un procedimiento general para definir el layout de una celda compleja, con estructura arbitraria.

La operación NAND tiene los transistores del plano P en paralelo y los del plano N en serie

La operación NOR tiene los transistores del plano N en paralelo y los del plano P en serie

- Transformación de la función en minitérminos:

- Suma de productos  $\Sigma(\pi)$  (Sumas de minitérminos)

- 2. Productos de sumas  $\pi(\Sigma)$  (productos de maxitérminos)

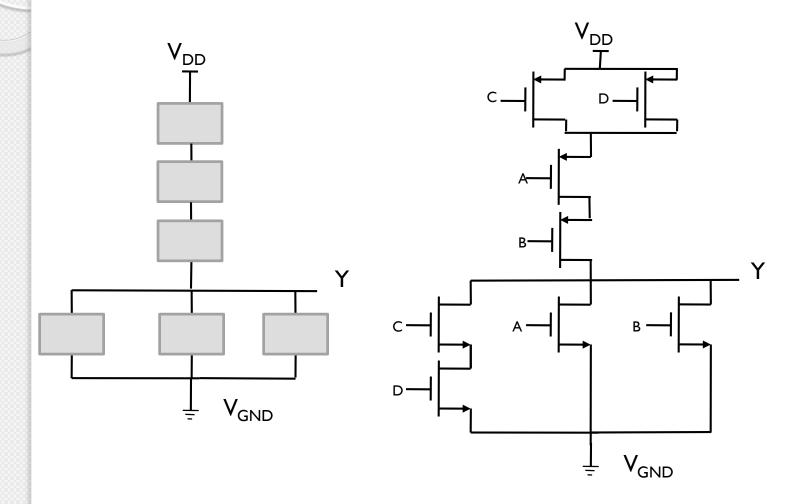

- Se trata de realizar una descomposición jerárquica a dos niveles.

Los minitérminos se denominan "grupos".

- Si se trata de sumas (OR) de minitérminos, los pondremos en serie en el plano P y en paralelo en en plano N

- Si se trata de productos (AND) de maxitérminos los pondremos en paralelo en el plano P y en serie en el plano N

- Si los minitérminos son productos de valores de entrada se colocarán transistores en serie en el plano N y en paralelo en el plano P

- Si los maxitérminos son sumas de valores de entrada se colocarán transistores en paralelo en el plano N y en serie en el plano P

- e) Finalmente se ajustan los inversores para cambiar polaridades. La salida es negada

$$Y = \overline{C \cdot D + A + B}$$

• Si consideramos la expresión como suma de productos, tiene estructura NOR:

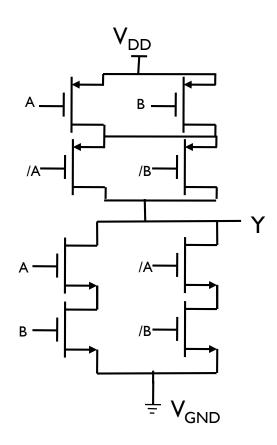

## 4. Puerta XOR

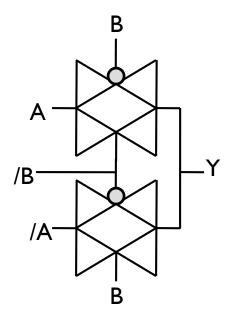

• Es una función que no se puede clasificar como las anteriores:  $Y = \overline{A} \cdot B + A \cdot \overline{B}$

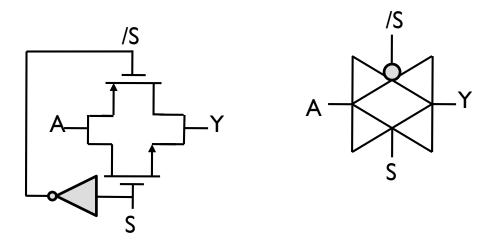

### 4. Puertas de transmisión

Se basa en el uso de dos transistores, un p y otro n en oposición

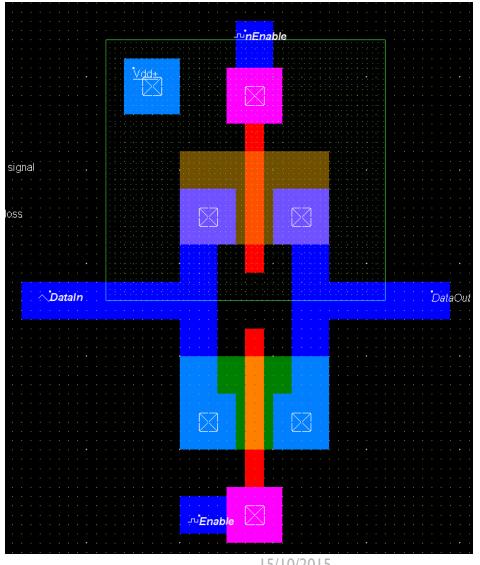

# 4.1 Layout de una PT

15/10/2015

# 4.2 Aplicaciones

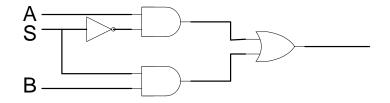

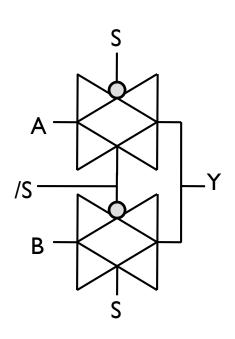

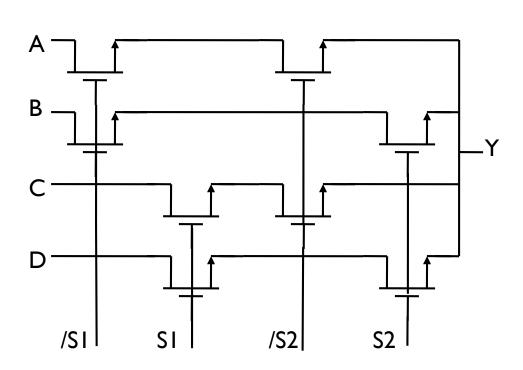

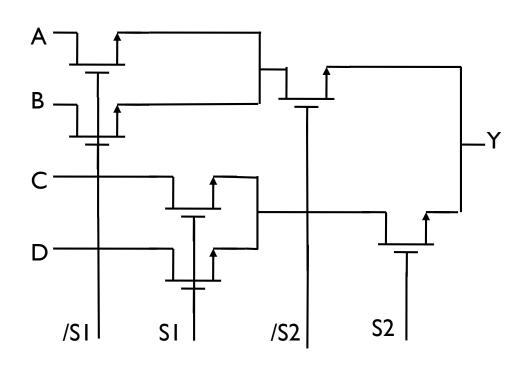

Multiplexor

## Otras puertas

Puerta OR

Puerta XOR